Design & specifications#

If you want to know how BeagleV-Fire board is designed and what are it’s high-level specifications then this chapter is for you. We are going to discuss each hardware design element in detail and provide high-level device specifications in a short and crisp form as well.

Tip

For hardware design files and schematic diagram you can checkout BeagleV-Fire GitLab repository: https://git.beagleboard.org/beaglev-fire/beaglev-fire

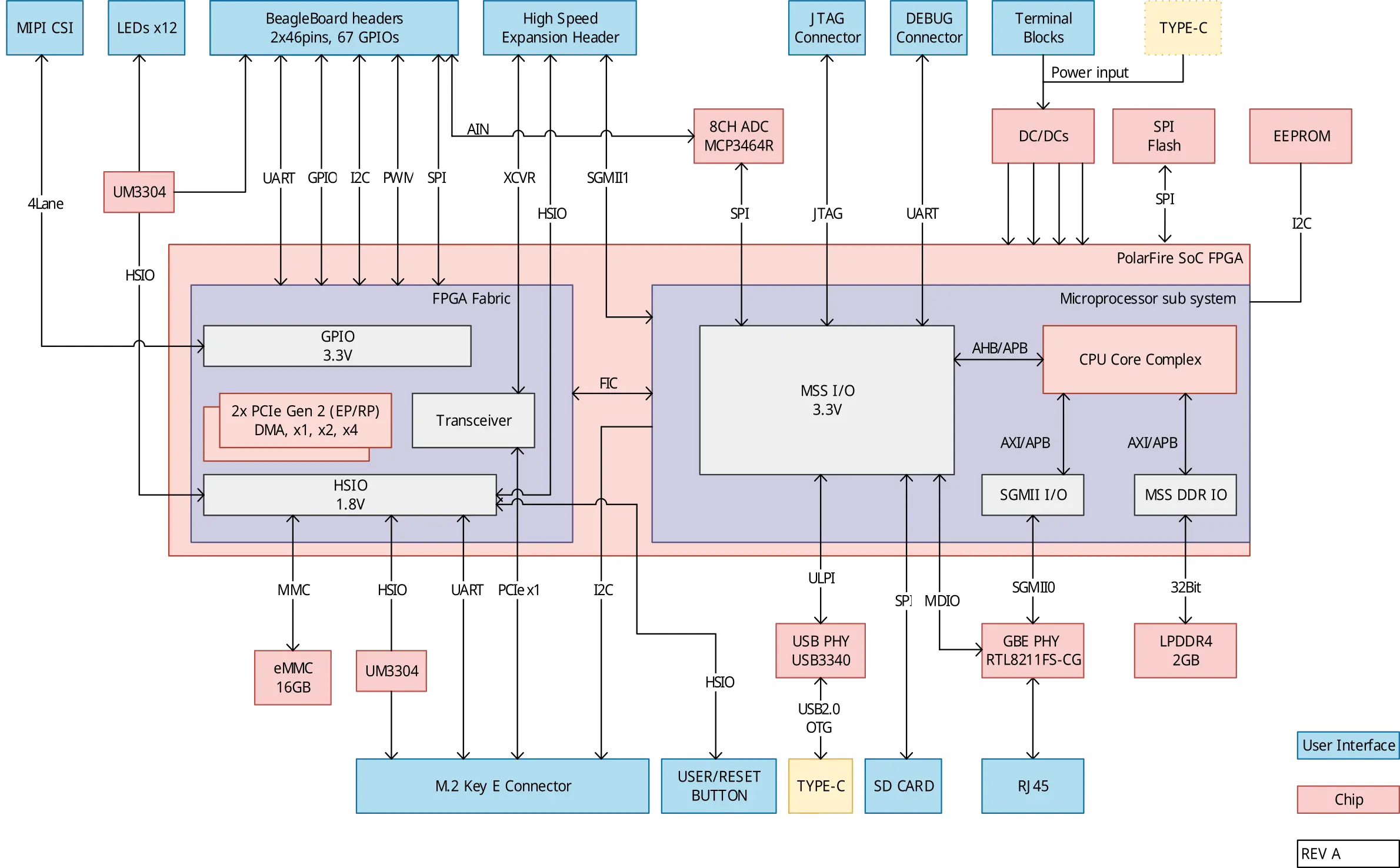

Block diagram#

Fig. 555 System block diagram#

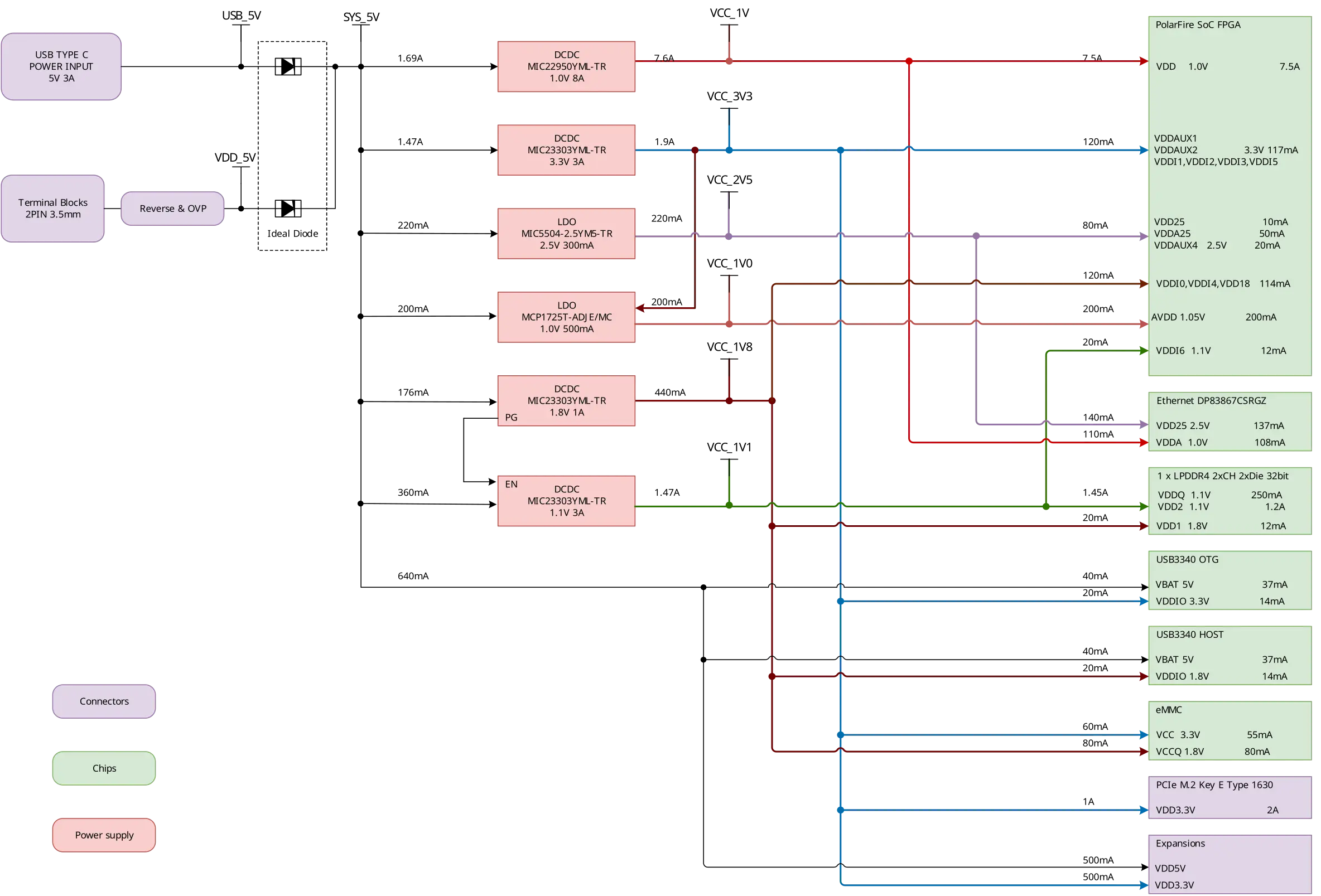

Fig. 556 Power tree diagram#

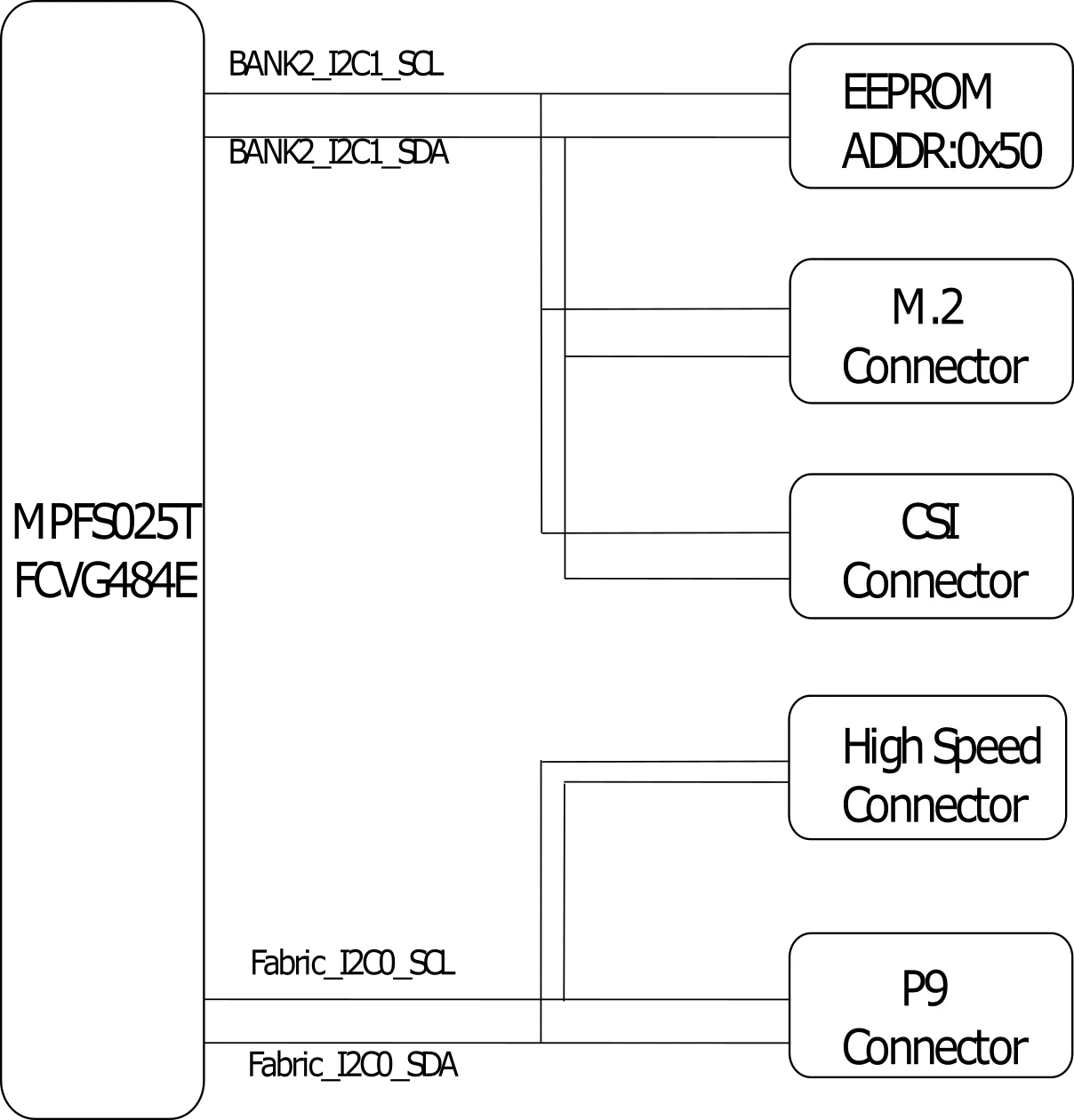

Fig. 557 I2C tree diagram#

System on Chip (SoC)#

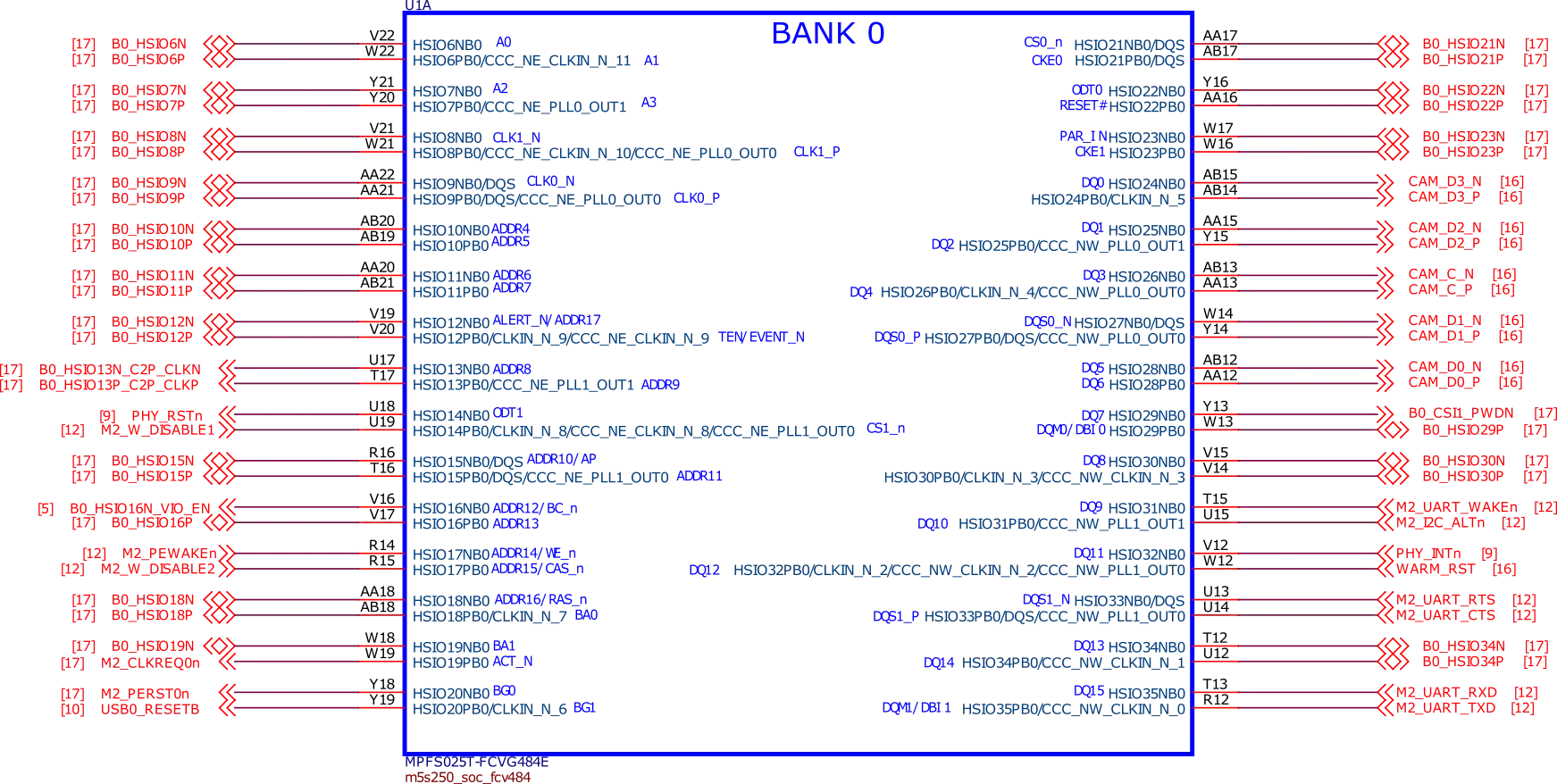

Fig. 558 SoC bank0#

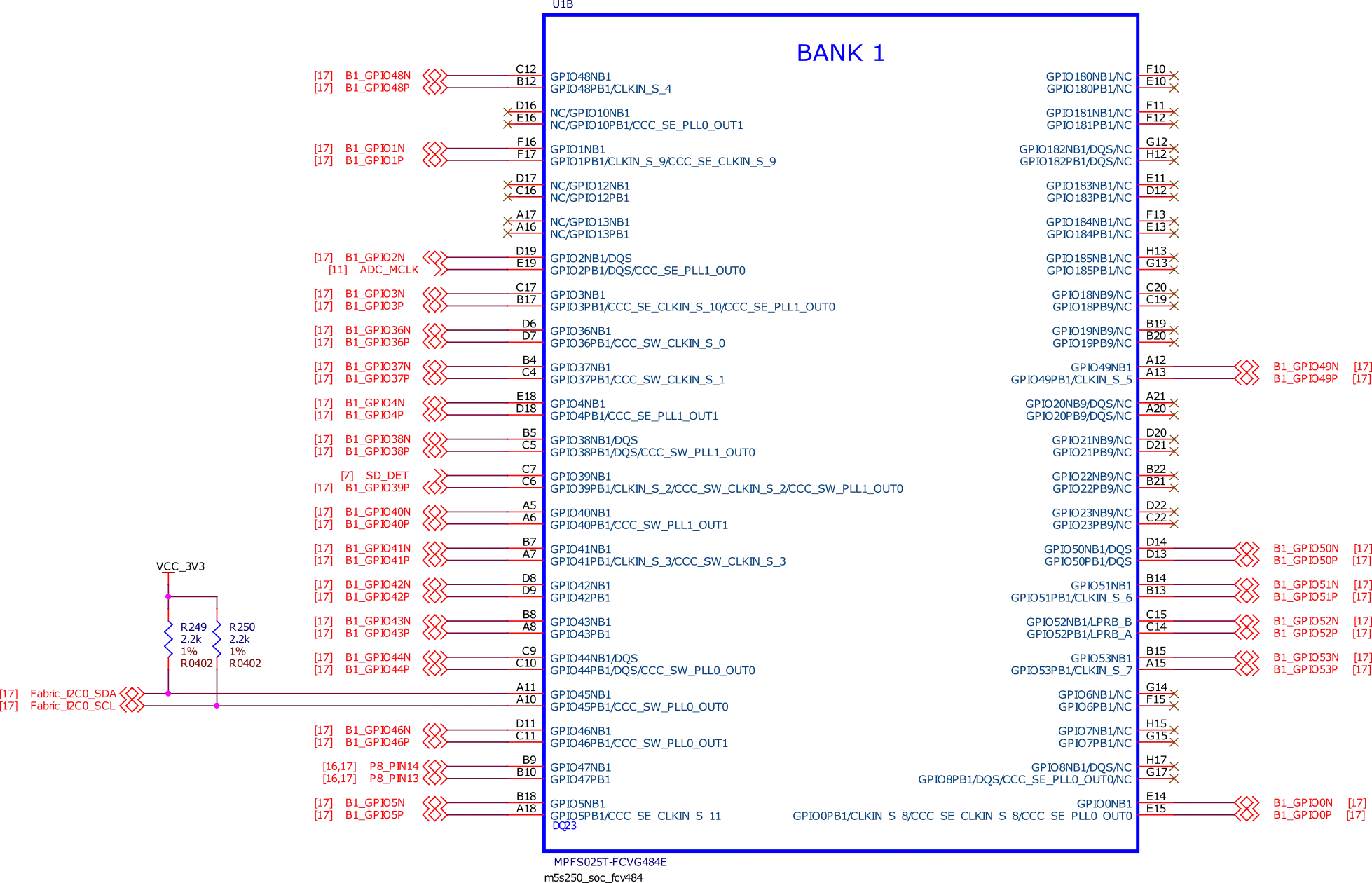

Fig. 559 SoC bank1#

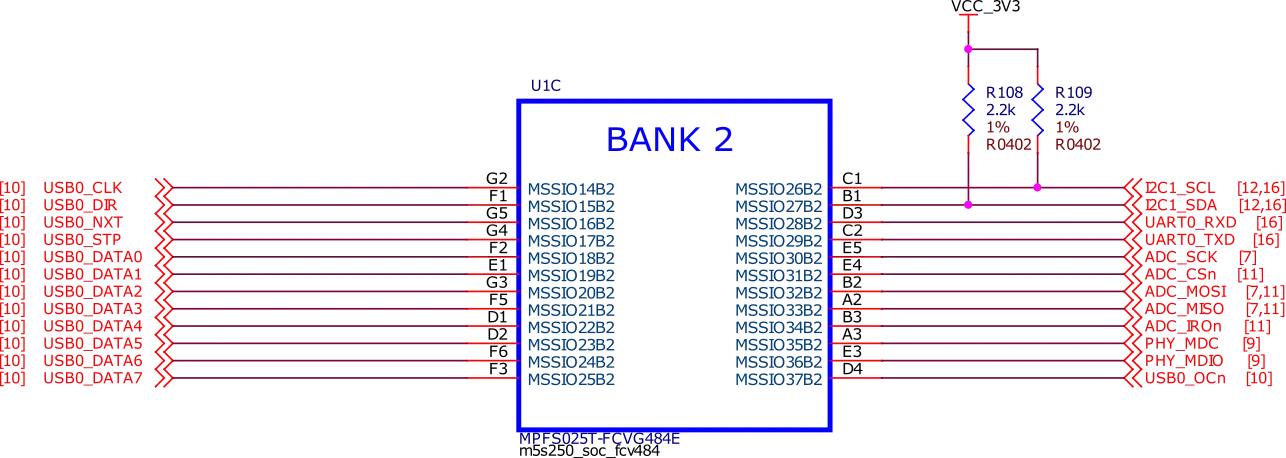

Fig. 560 SoC bank2#

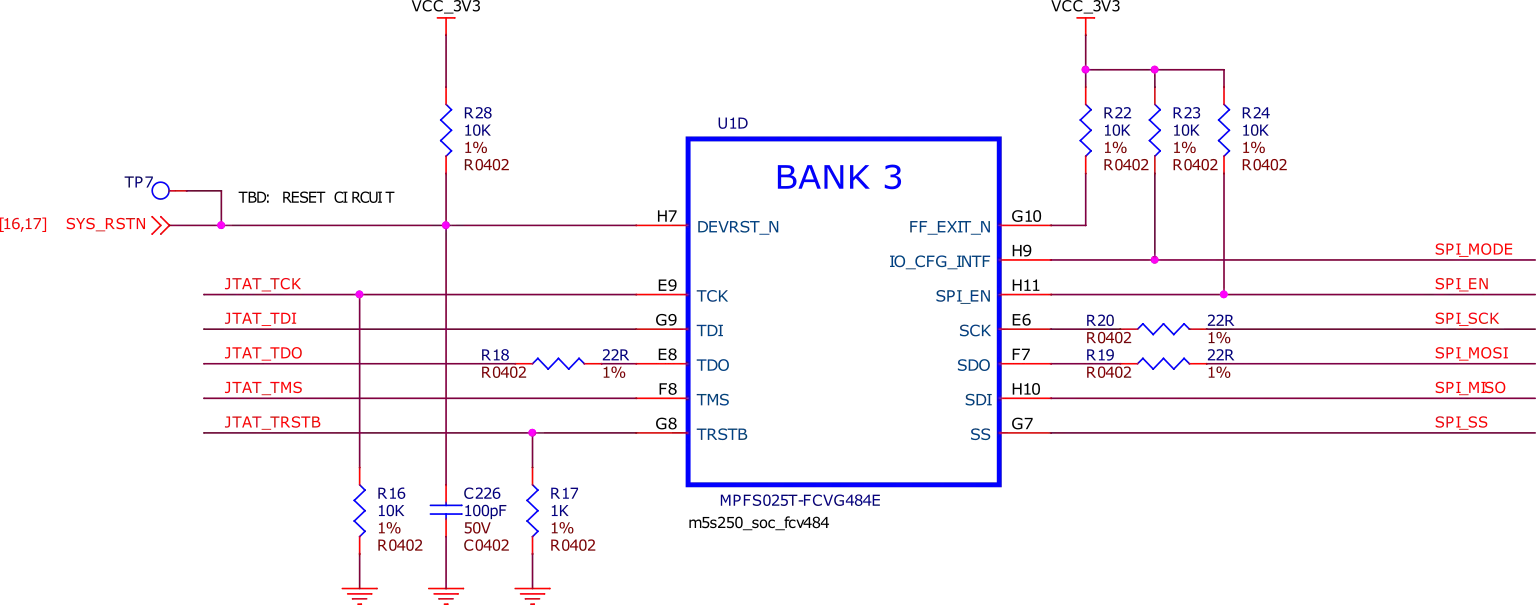

Fig. 561 SoC bank3#

Fig. 562 SoC bank4#

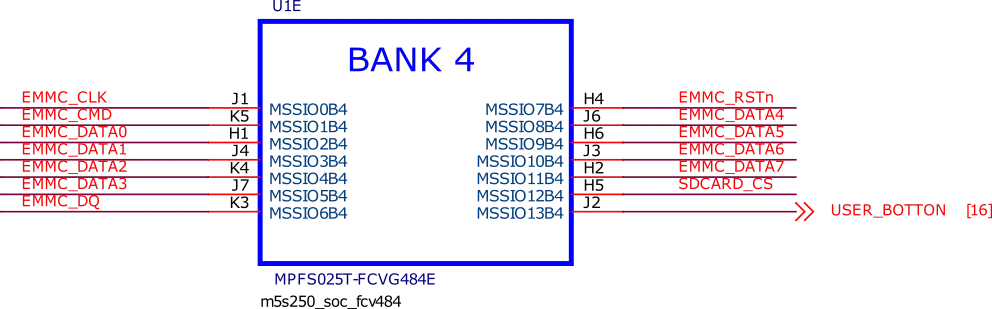

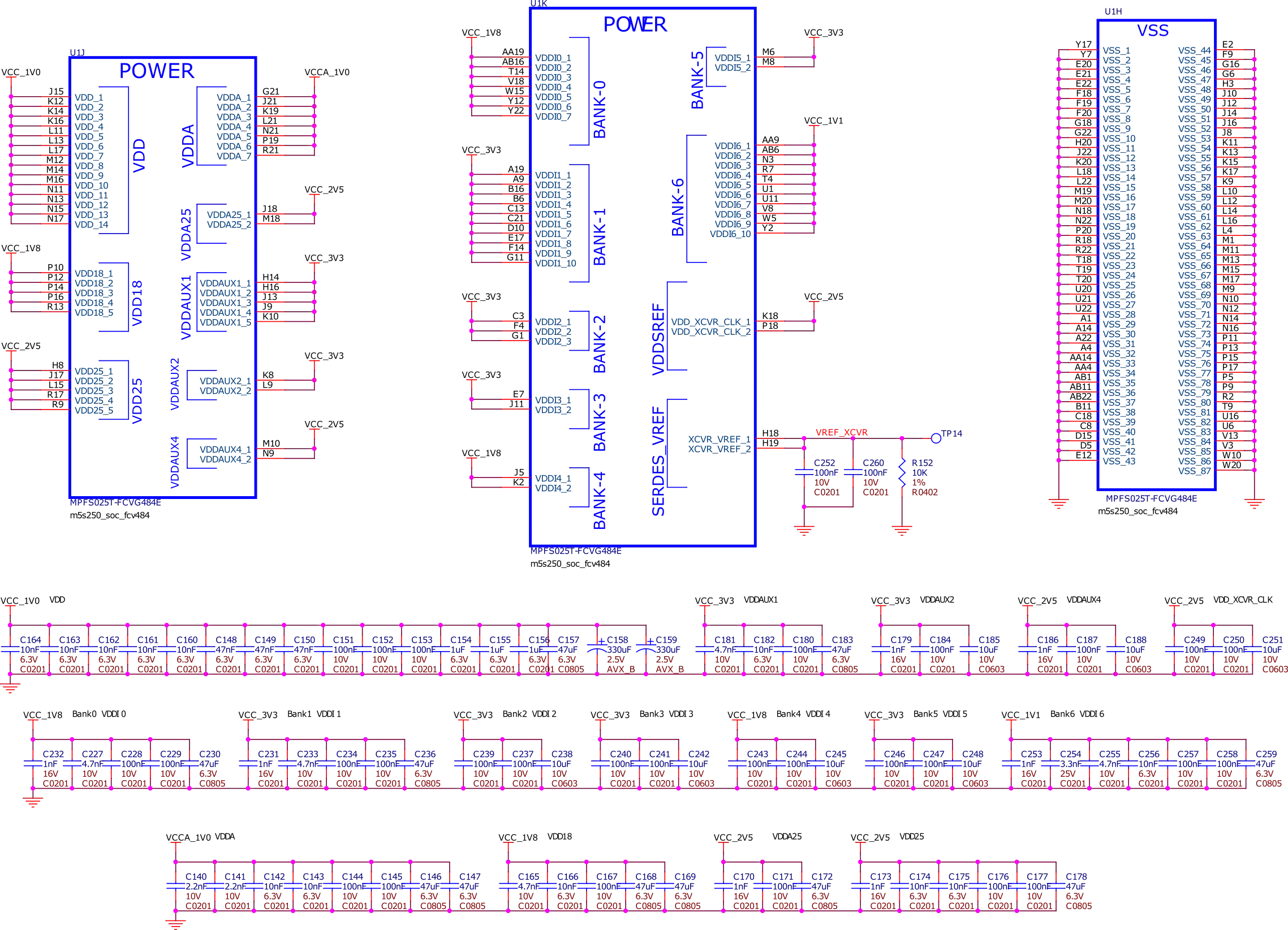

Fig. 563 SoC power#

Power management#

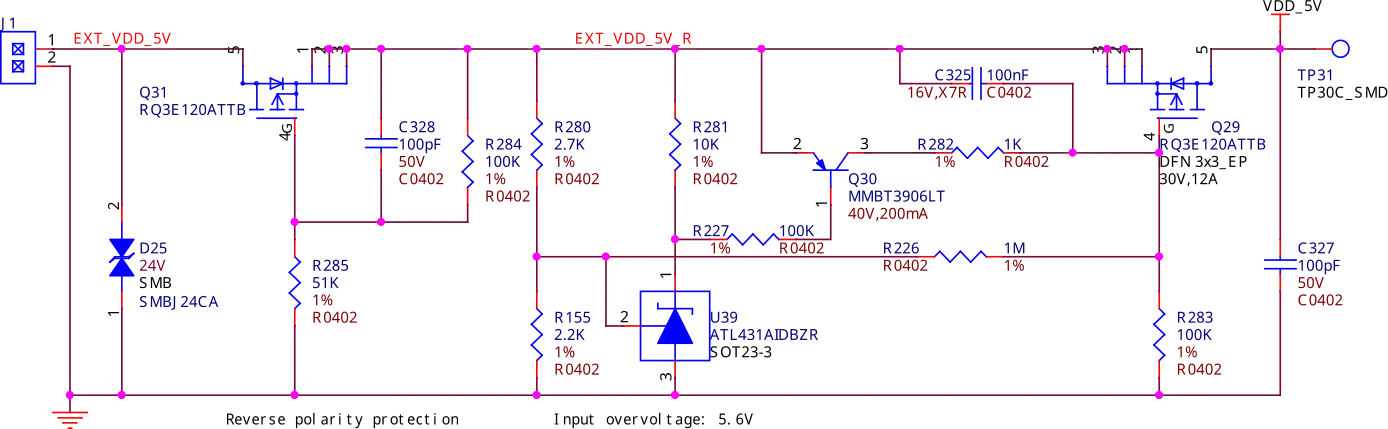

Fig. 564 DC 5V input#

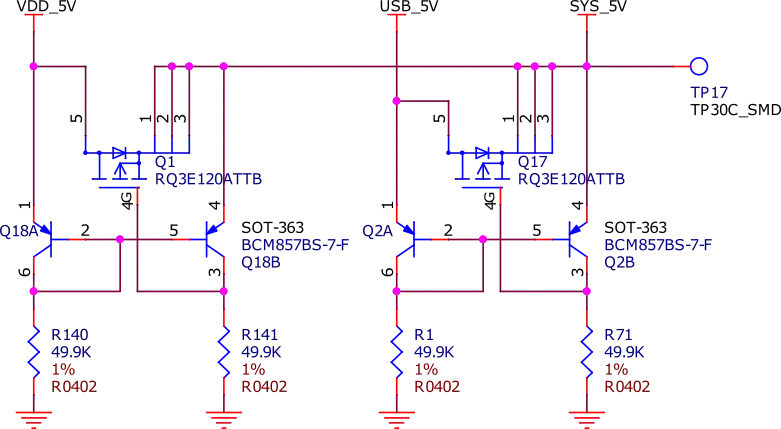

Fig. 565 Ideal diode#

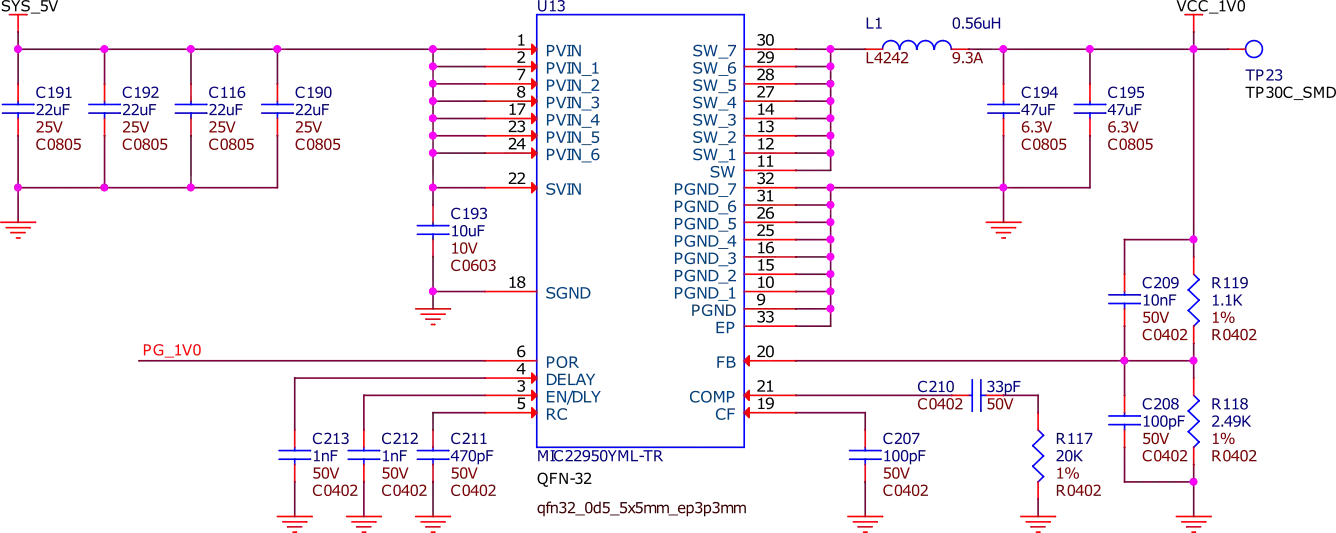

Fig. 566 VCC 1V0#

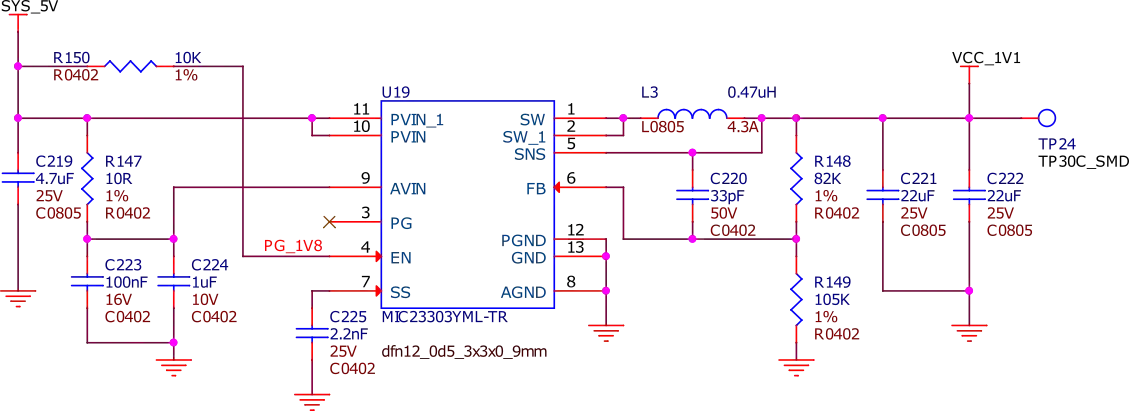

Fig. 567 VCC 1V1#

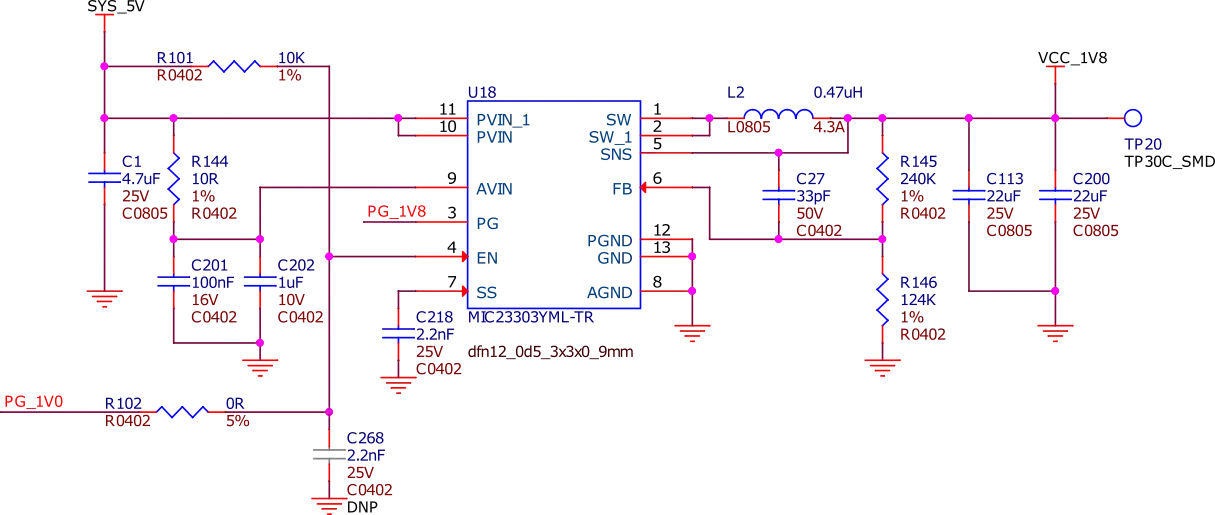

Fig. 568 VCC 1V8#

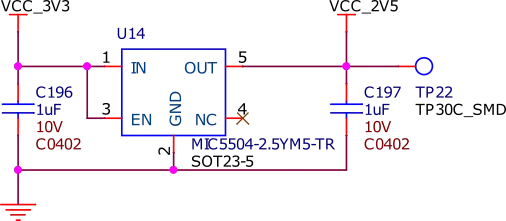

Fig. 569 VCC 2V5#

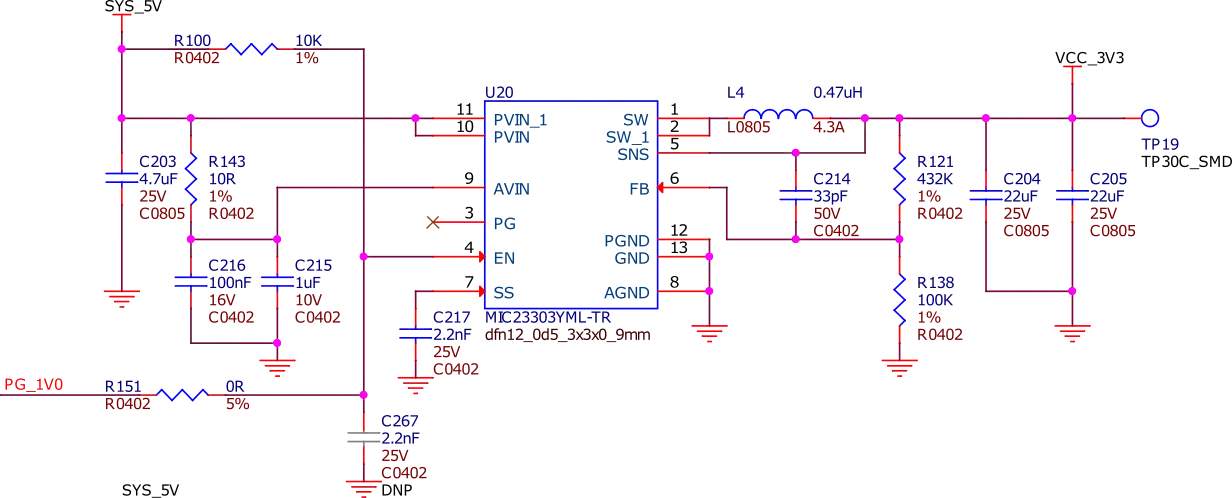

Fig. 570 VCC 3V3#

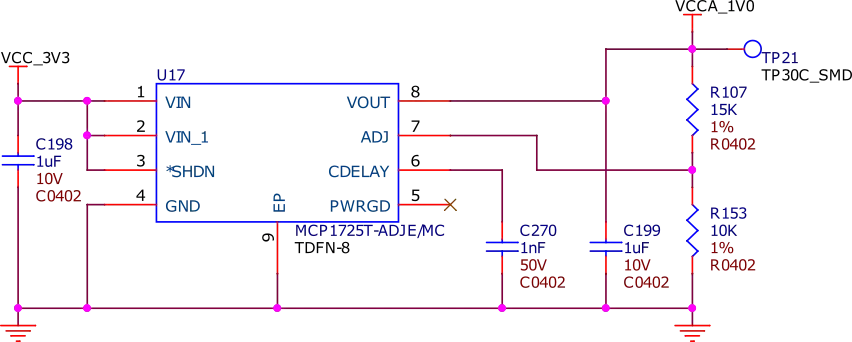

Fig. 571 VCCA 1V0#

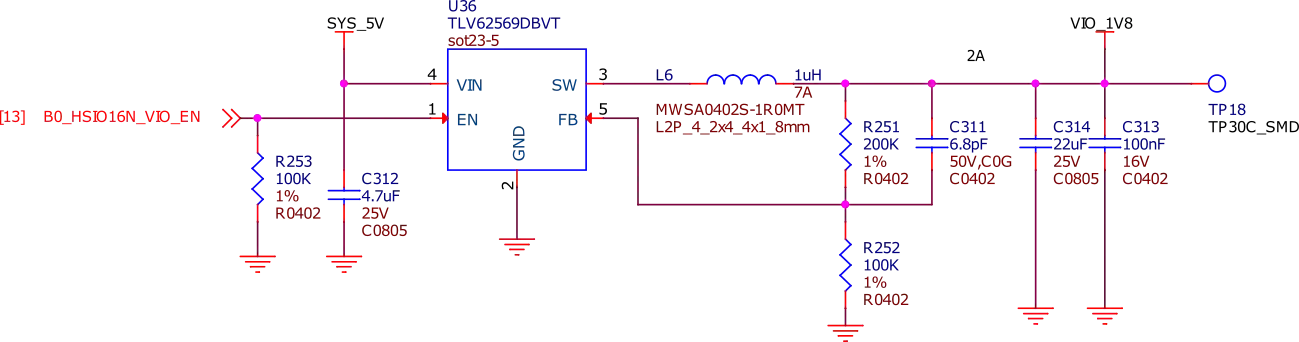

Fig. 572 VIO enable#

General Connectivity and Expansion#

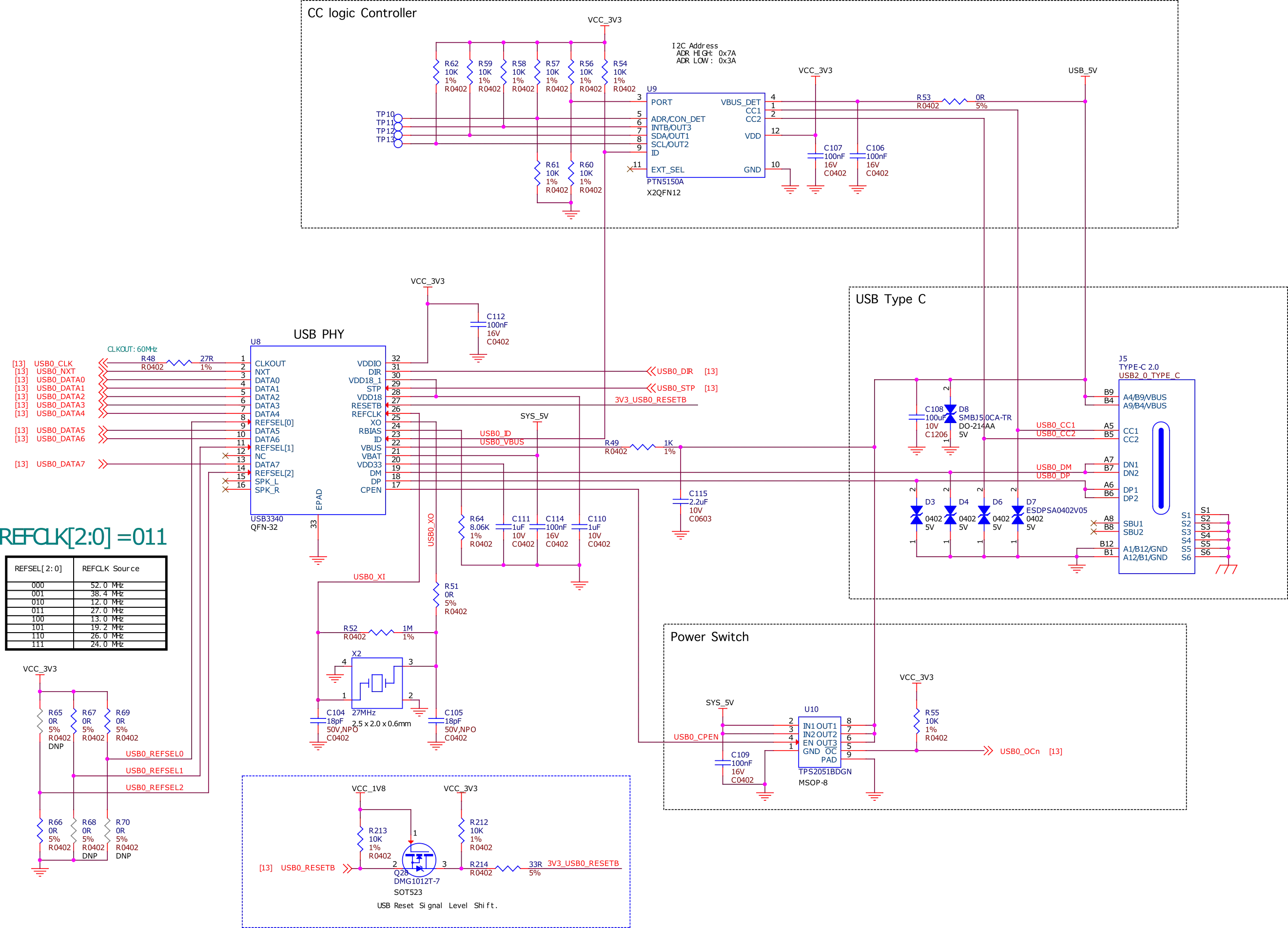

USB-C port#

Fig. 573 USB C#

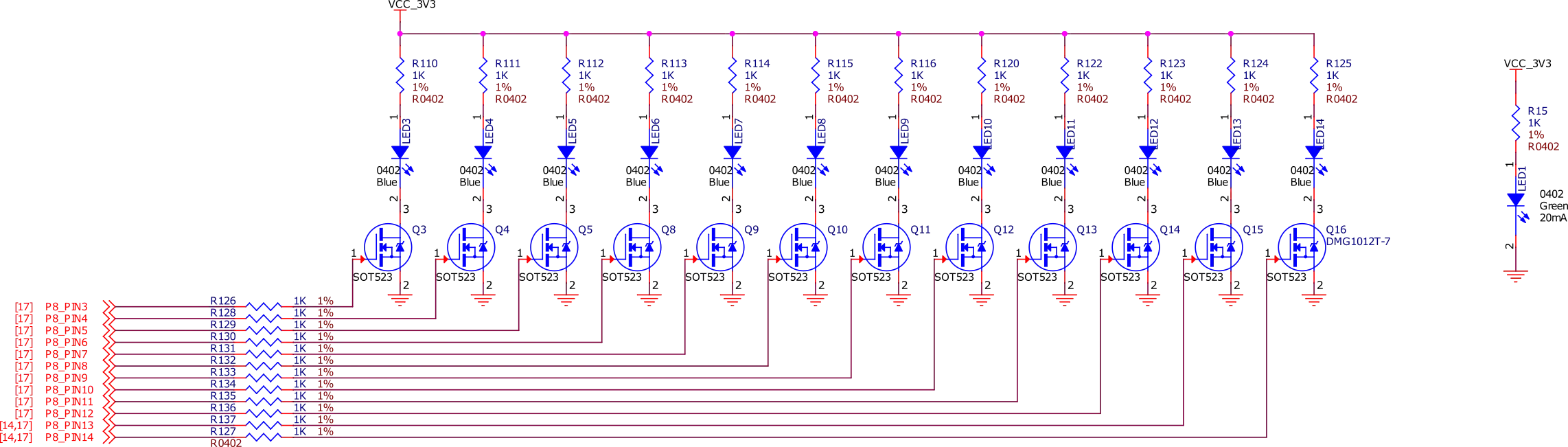

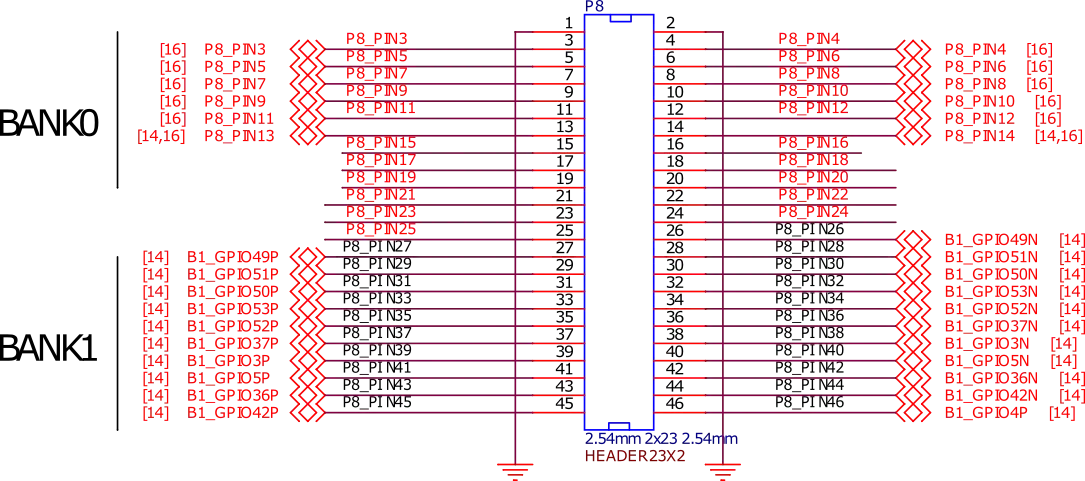

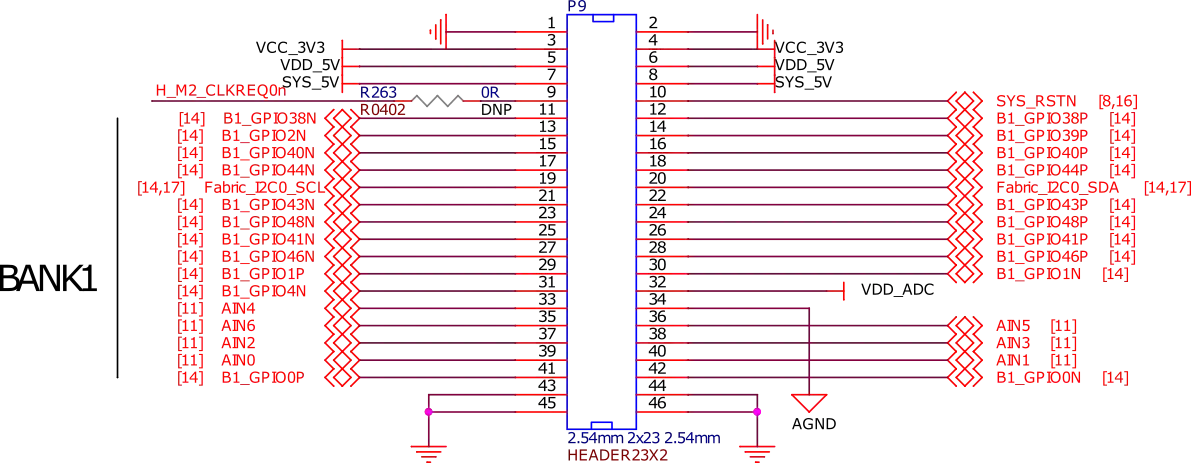

P8 & P9 cape header pins#

Fig. 574 P8 cape header#

Fig. 575 P9 cape header#

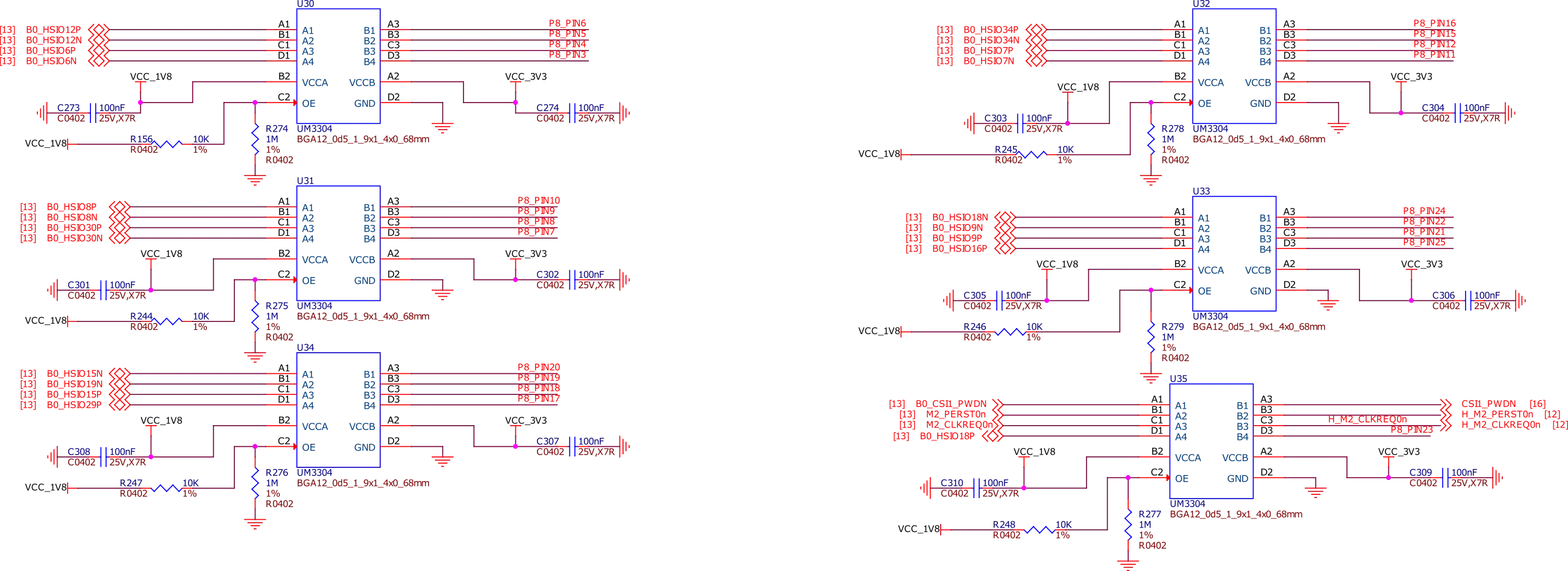

Fig. 576 Cape header voltage level translator#

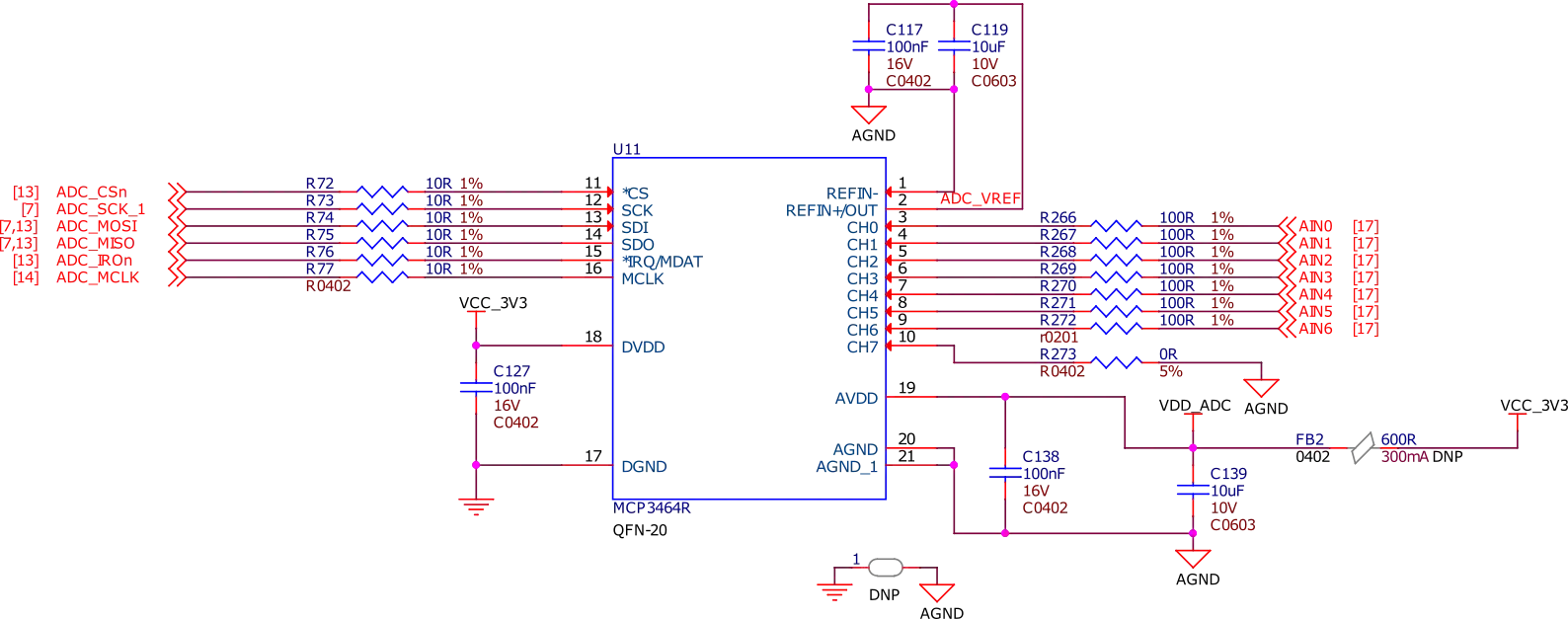

ADC#

Fig. 577 16bit Delta-Sigma ADC#

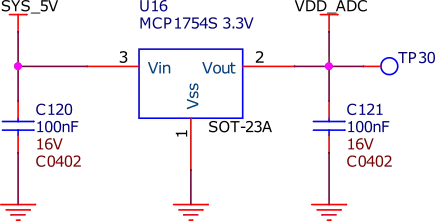

Fig. 578 ADC LDO power supply#

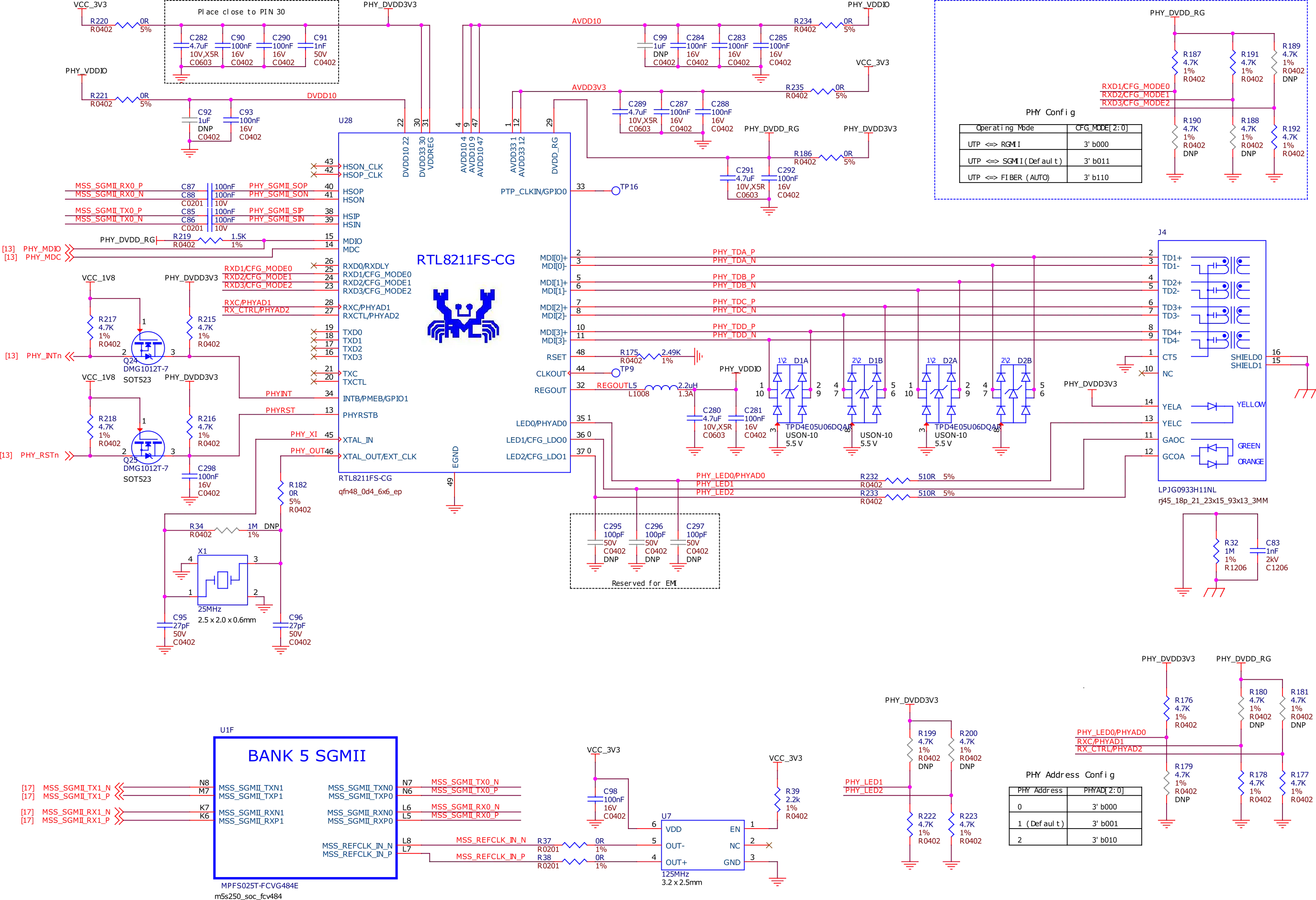

Connectivity#

Ethernet#

Fig. 582 Gigabit ethernet#

Memory, Media and Data storage#

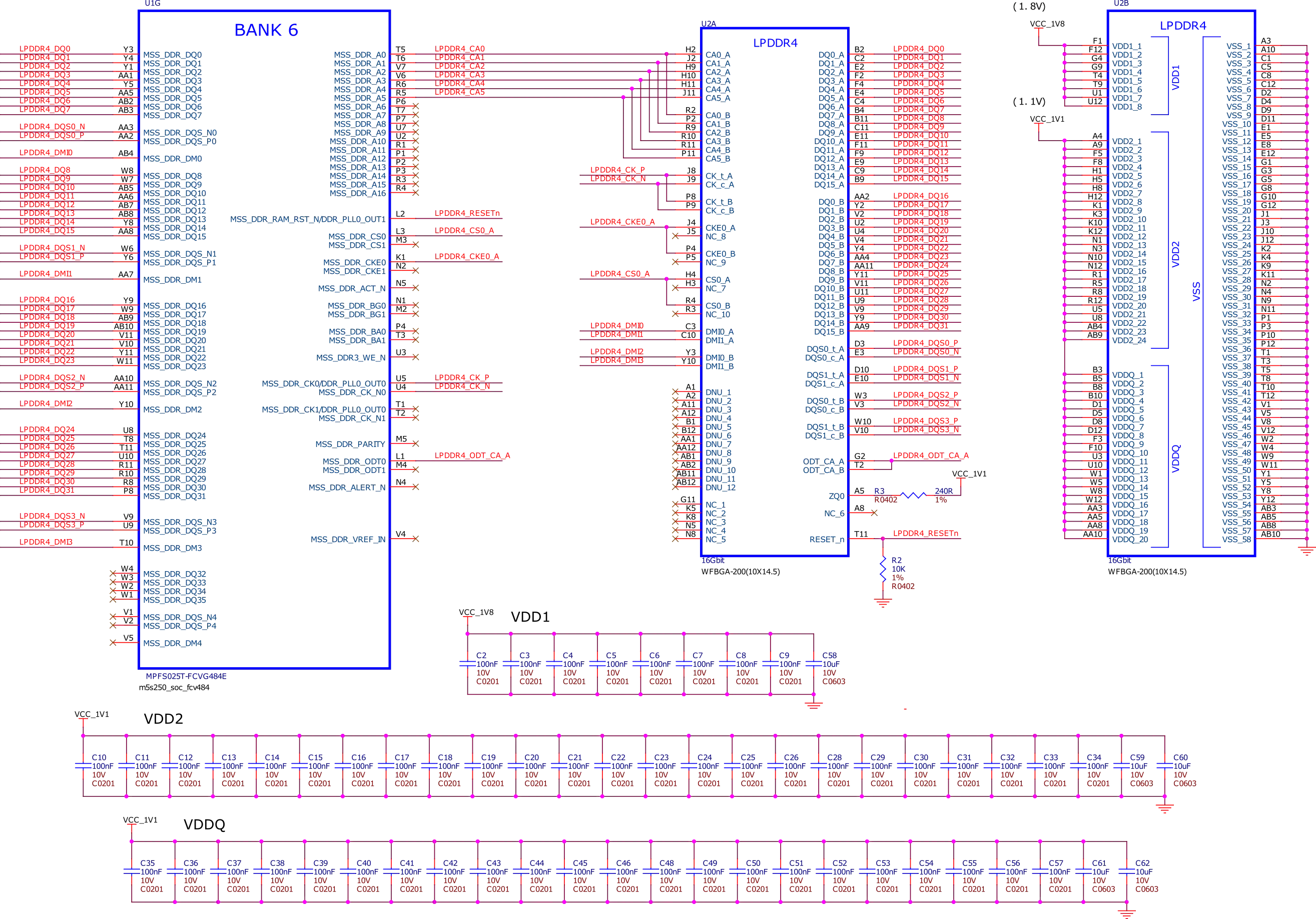

DDR memory#

Fig. 583 LPDDR memory#

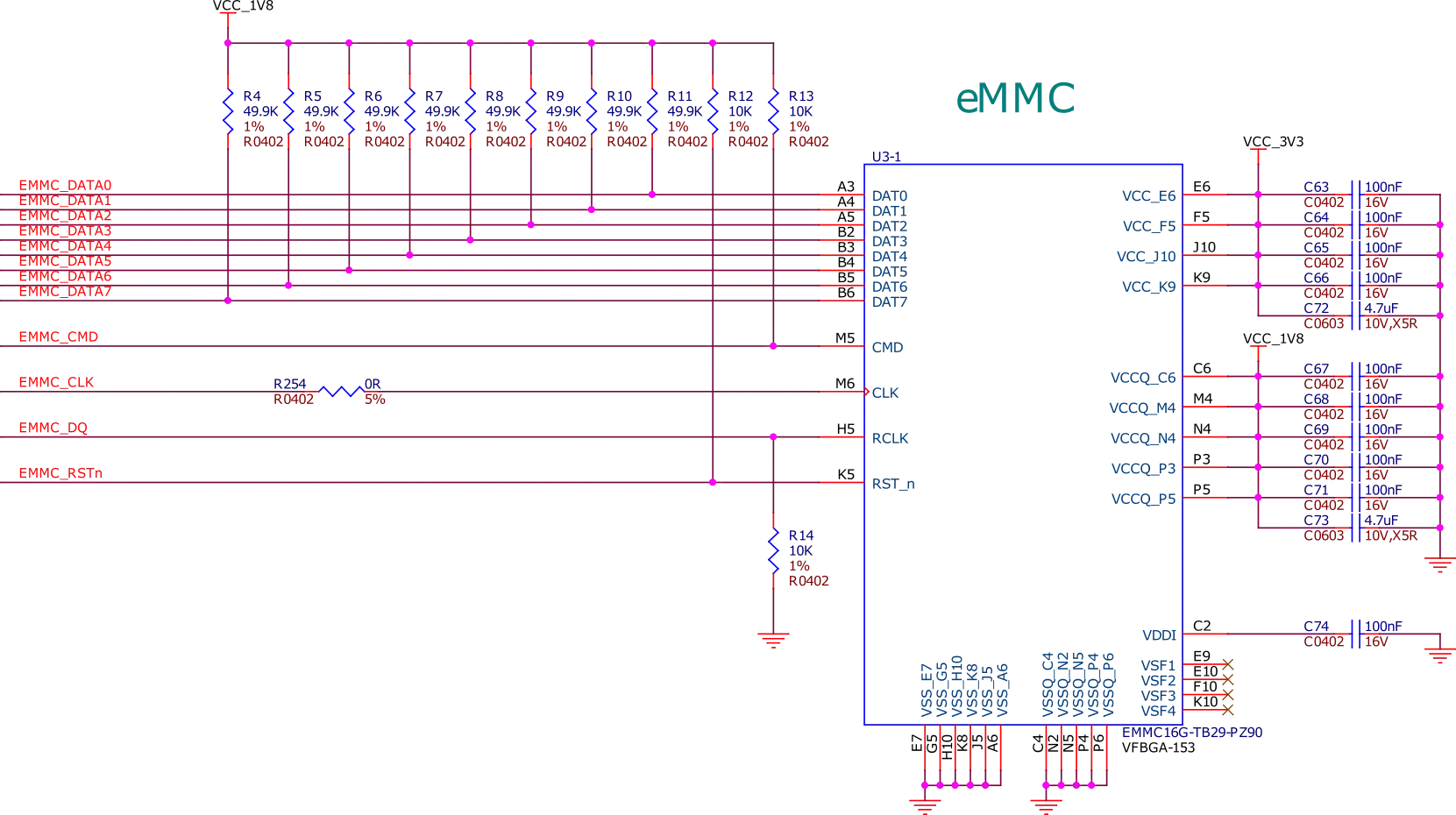

eMMC#

Fig. 584 EMMC flash storage#

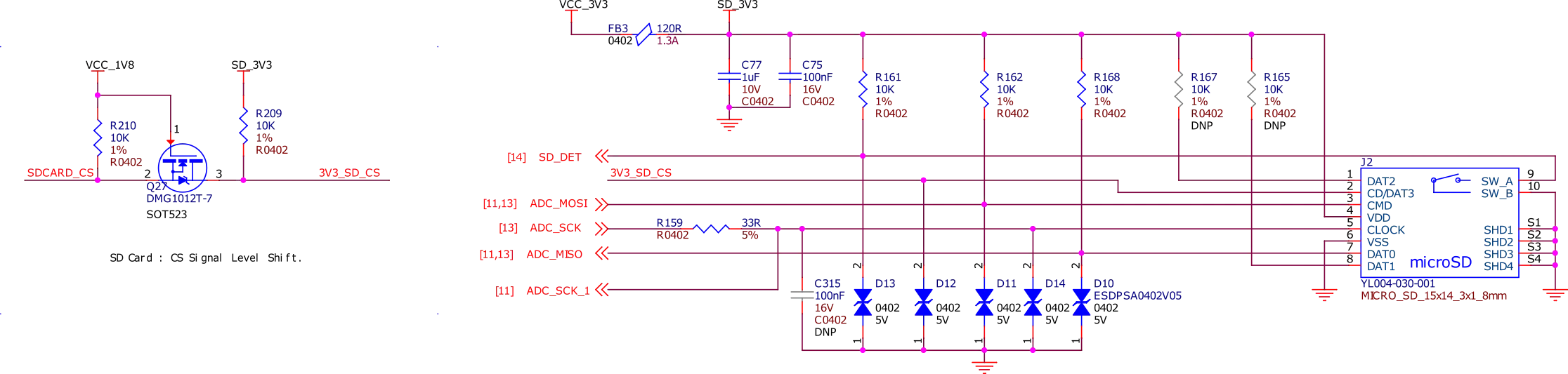

microSD#

Fig. 585 SD Card socket#

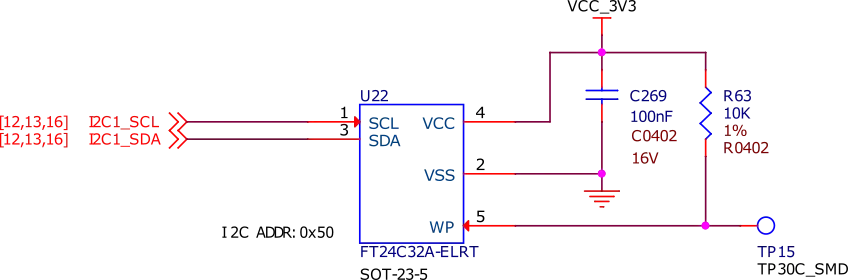

EEPROM#

Fig. 586 EEPROM#

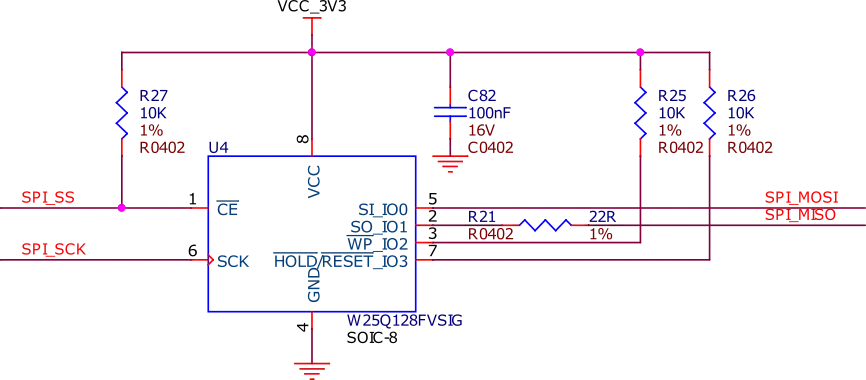

SPI flash#

Fig. 587 SPI Flash#

Multimedia I/O#

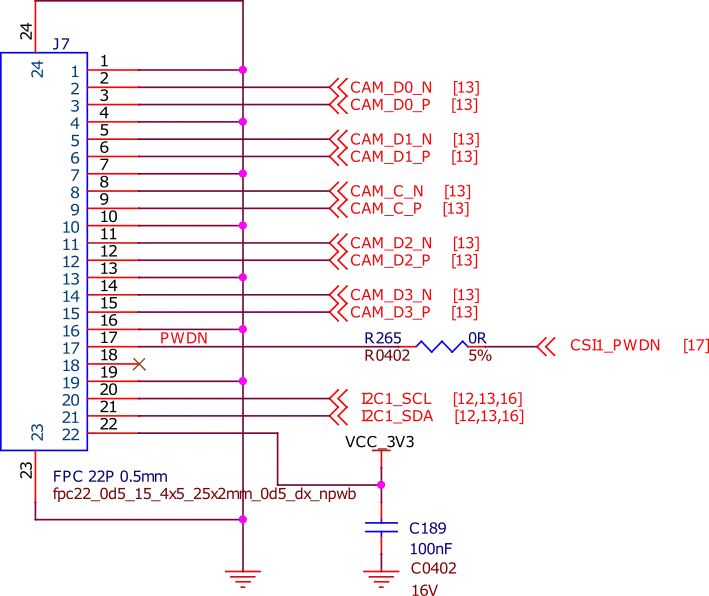

CSI#

Fig. 588 CSI#

Debug#

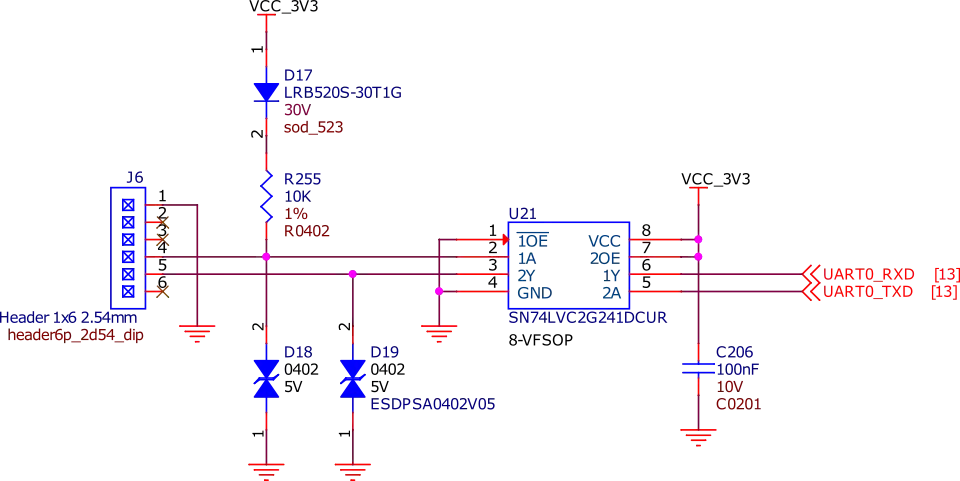

UART debug port#

Fig. 589 UART debug header#

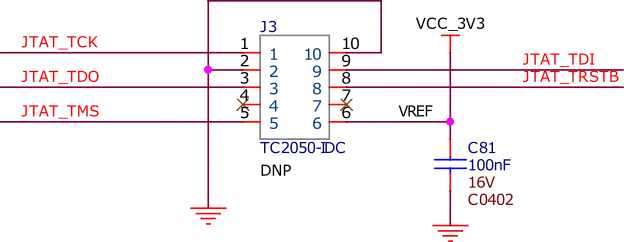

JTAG debug port#

Fig. 590 JTAG debug header#

Mechanical Specifications#

Parameter |

Values |

|---|---|

Size |

86.38 * 54.61 * 18.8 mm |

Max heigh |

18.8 mm |

PCB Size |

86.38 * 54.6 mm |

PCB Layers |

12 Layers |

PCB Thickness |

1.6 mm |

RoHS compliant |

Yes |

Gross Weight |

106 g |

Net weight |

45.8 g |