Detailed Hardware Design#

This section provides a detailed description of the Hardware design. This can be useful for interfacing, writing drivers, or using it to help modify specifics of your own design.

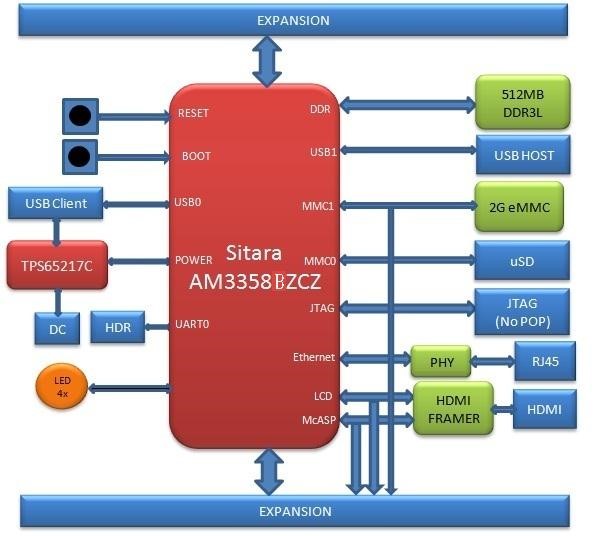

Fig. 438 BeagleBone Black Block Diagram#

Power Section#

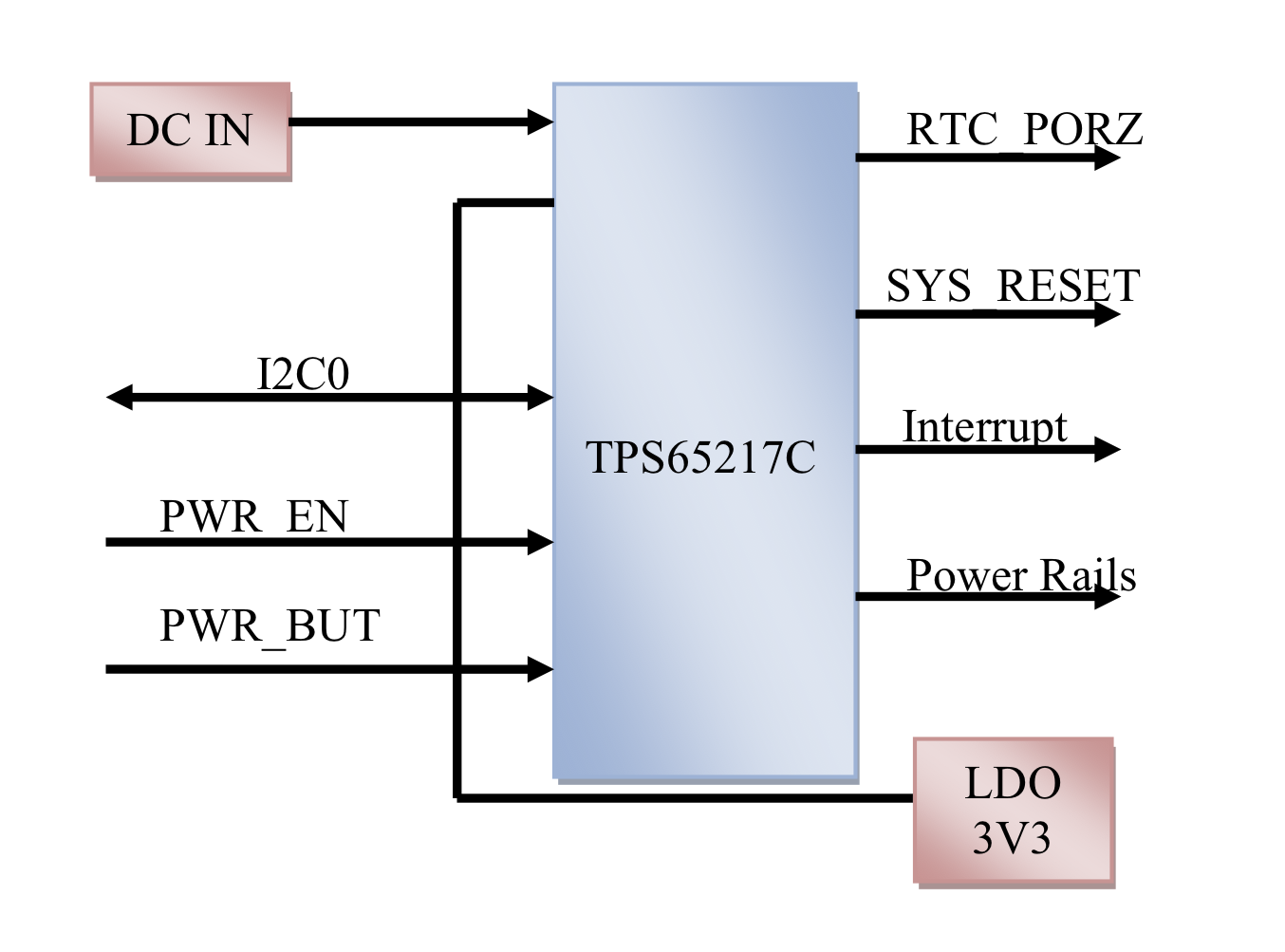

Fig. 439 High Level Power Block Diagram#

This section describes the power section of the design and all the functions performed by the TPS65217C.

TPS65217C PMIC#

The main Power Management IC (PMIC) in the system is the TPS65217C which is a single chip power management IC consisting of a linear dual-input power path, three step-down converters, and four LDOs. LDO stands for Low Drop Out. If you want to know more about an LDO, you can go to http://en.wikipedia.org/wiki/Low-dropout_regulator .If you want to learn more about step-down converters, you can go to

http://en.wikipedia.org/wiki/DC-to-DC_converter

The system is supplied by a USB port or DC adapter. Three high-efficiency 2.25MHz step-down converters are targeted at providing the core voltage, MPU, and memory voltage for the board.

The step-down converters enter a low power mode at light load for maximum efficiency across the widest possible range of load currents. For low-noise applications the devices can be forced into fixed frequency PWM using the I2C interface. The step-down converters allow the use of small inductors and capacitors to achieve a small footprint solution size.

LDO1 and LDO2 are intended to support system standby mode. In normal operation, they can support up to 100mA each. LDO3 and LDO4 can support up to 285mA each.

By default only LDO1 is always ON but any rail can be configured to remain up in SLEEP state. In particular the DCDC converters can remain up in a low-power PFM mode to support processor suspend mode. The TPS65217C offers flexible power-up and power-down sequencing and several house-keeping functions such as power-good output, pushbutton monitor, hardware reset function and temperature sensor to protect the battery.

For more information on the TPS65217C, refer to http://www.ti.com/product/tps65217C

Fig. 440 TPS65217C Block Diagram#

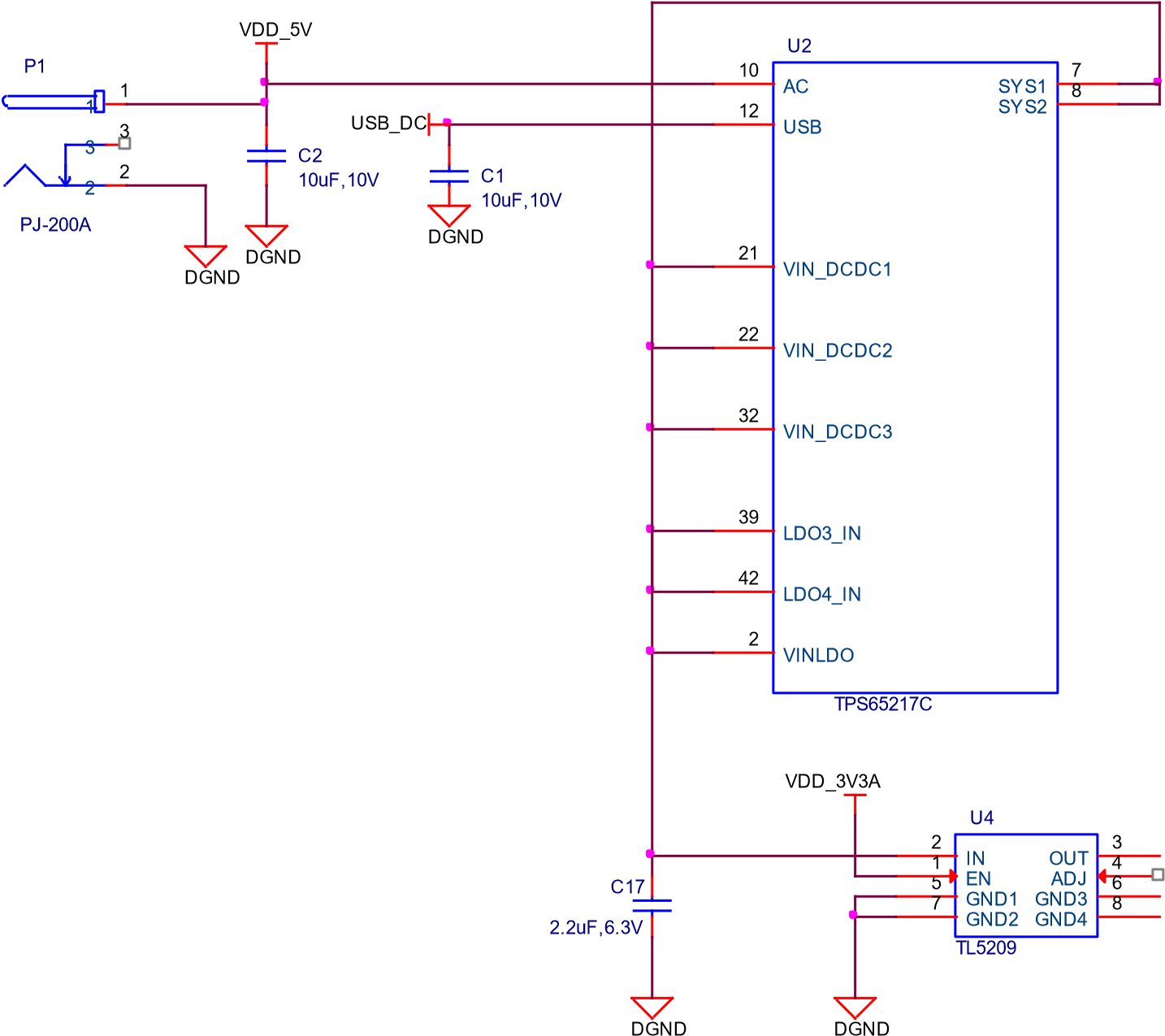

DC Input#

Fig. 441 TPS65217 DC Connection#

A 5VDC supply can be used to provide power to the board. The power supply current depends on how many and what type of add-on boards are connected to the board. For typical use, a 5VDC supply rated at 1A should be sufficient. If heavier use of the expansion headers or USB host port is expected, then a higher current supply will be required.

The connector used is a 2.1MM center positive x 5.5mm outer barrel. The 5VDC rail is connected to the expansion header. It is possible to power the board via the expansion headers from an add-on card. The 5VDC is also available for use by the add-on cards when the power is supplied by the 5VDC jack on the board.

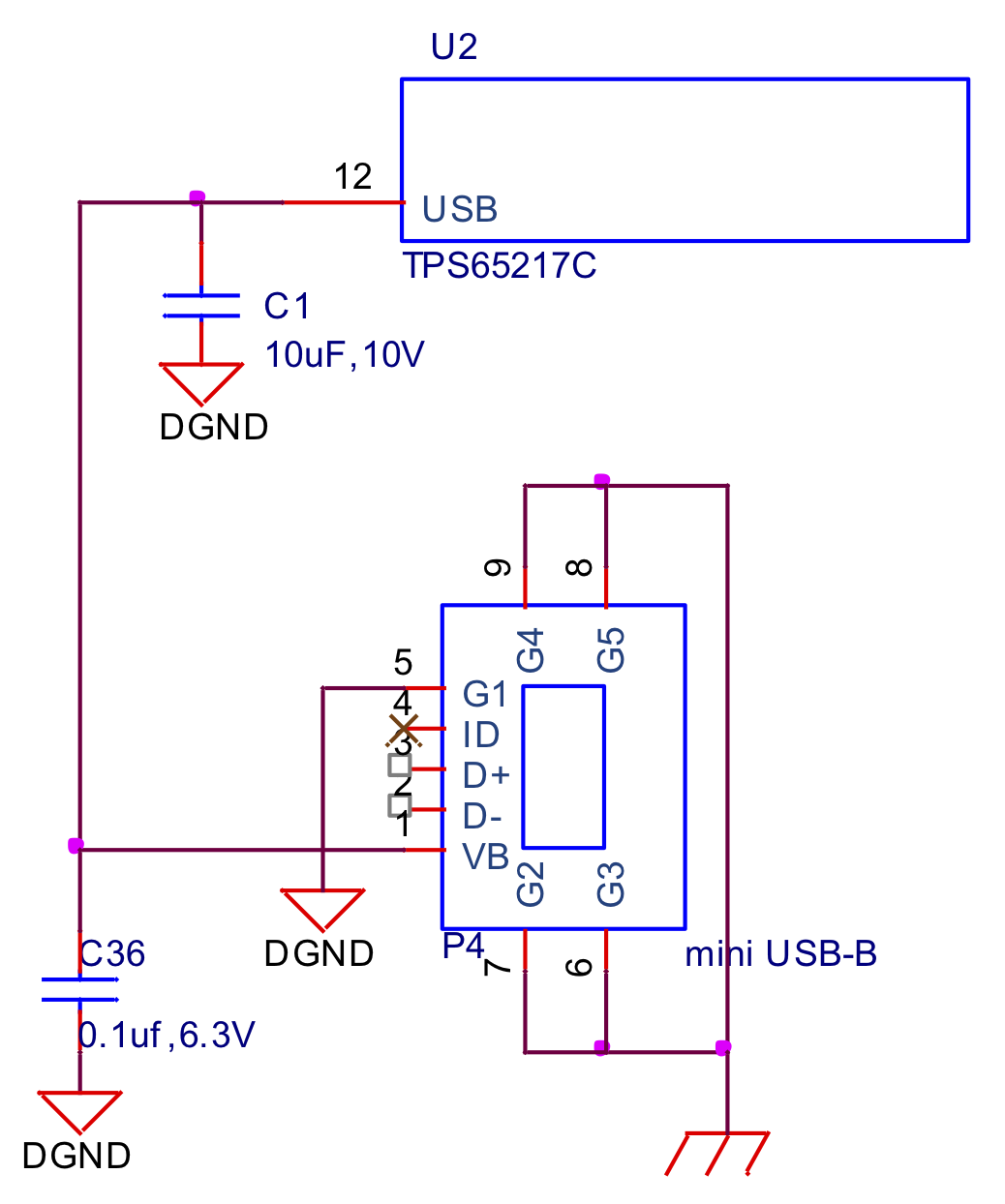

USB Power#

The board can also be powered from the USB port. A typical USB port is limited to 500mA max. When powering from the USB port, the VDD_5V rail is not provided to the expansion headers, so capes that require the 5V rail to supply the cape direct, bypassing the TPS65217C, will not have that rail available for use. The 5VDC supply from the USB port is provided on the SYS_5V, the one that comes from the**TPS65217C**, rail of the expansion header for use by a cape. Figure 24 is the connection of the USB power input on the PMIC.

Fig. 442 USB Power Connections#

Power Selection#

The selection of either the 5VDC or the USB as the power source is handled internally to the TPS65217C and automatically switches to 5VDC power if both are connected. SW can change the power configuration via the I2C interface from the processor. In addition, the SW can read the**TPS65217C** and determine if the board is running on the 5VDC input or the USB input. This can be beneficial to know the capability of the board to supply current for things like operating frequency and expansion cards.

It is possible to power the board from the USB input and then connect the DC power supply. The board will switch over automatically to the DC input.

Battery Access Pads#

Four pads are provided on the board to allow access to the battery pins on the TPS65217C. The pads can be loaded with a 4x4 header or you may just wire a battery into the pads. In addition they could provide access via a cape if desired. The four signals are listed below in table-3 .

PIN |

DESIGNATION |

FUNCTION |

|---|---|---|

BAT |

TP5 |

Battery connection point |

SENSE |

TP6 |

Battery voltage sense input, connect to BAT directly at the battery terminal. |

TS |

TP7 |

Temperature sense input. Connect to NTC thermistor to sense battery temperature. |

GND |

TP8 |

System ground. |

There is no fuel gauge function provided by the TPS65217C. That would need to be added if that function was required. If you want to add a fuel gauge, an option is to use 1-wire SPI or I2C device. You will need to add this using the expansion headers and place it on an expansion board.

NOTE: Refer to the TPS65217C documentation + before connecting anything to these pins.

Power Consumption#

The power consumption of the board varies based on power scenarios and the board boot processes. Measurements were taken with the board in the following configuration:

DC powered and USB powered

HDMI monitor connected

USB HUB

4GB USB flash drive

Ethernet connected @ 100M

Serial debug cable connected

MODE |

USB |

DC |

DC+USB |

|---|---|---|---|

Reset |

TBD |

TBD |

TBD |

Idling @ UBoot |

210 |

210 |

210 |

Kernel Booting (Peak) |

460 |

460 |

460 |

Kernel Idling |

350 |

350 |

350 |

Kernel Idling Display Blank |

280 |

280 |

280 |

Loading a Webpage |

430 |

430 |

430 |

The current will fluctuate as various activates occur, such as the LEDs on and microSD/eMMC accesses.

Processor Interfaces#

The processor interacts with the TPS65217C via several different signals. Each of these signals is described below.

I2C0

I2C0 is the control interface between the processor and the TPS65217C. It allows the processor to control the registers inside the TPS65217C for such things as voltage scaling and switching of the input rails.

PMIC_POWR_EN

On power up the VDD_RTC rail activates first. After the RTC circuitry in the processor has activated it instructs the**TPS65217C** to initiate a full power up cycle by activating the PMIC_POWR_EN signal by taking it HI. When powering down, the processor can take this pin low to start the power down process.

LDO_GOOD

This signal connects to the RTC_PORZn signal, RTC power on reset. The small n indicates that the signal is an active low signal. Word processors seem to be unable to put a bar over a word so the **n* is commonly used in electronics. As the RTC circuitry comes up first, this signal indicates that the LDOs, the 1.8V VRTC rail, is up and stable. This starts the power up process.

PMIC_PGOOD

Once all the rails are up, the PMIC_PGOOD signal goes high. This releases the PORZn signal on the processor which was holding the processor reset.

WAKEUP

The WAKEUP signal from the TPS65217C is connected to the EXT_WAKEUP signal on the processor. This is used to wake up the processor when it is in a sleep mode. When an event is detected by the TPS65217C, such as the power button being pressed, it generates this signal.

PMIC_INT

The PMIC_INT signal is an interrupt signal to the processor. Pressing the power button will send an interrupt to the processor allowing it to implement a power down mode in an orderly fashion, go into sleep mode, or cause it to wake up from a sleep mode. All of these require SW support.

Power Rails#

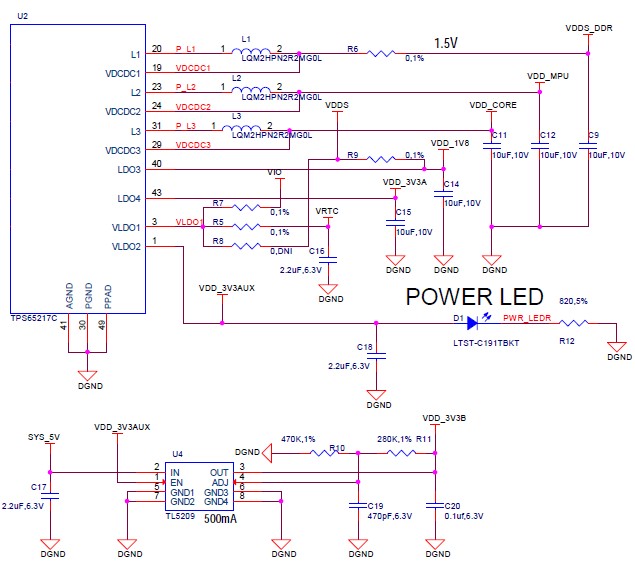

Fig. 443 Power Rails#

VRTC Rail

The VRTC rail is a 1.8V rail that is the first rail to come up in the power sequencing. It provides power to the RTC domain on the processor and the I/O rail of the TPS65217C. It can deliver up to 250mA maximum.

VDD_3V3A Rail

The VDD_3V3A rail is supplied by the TPS65217C and provides the 3.3V for the processor rails and can provide up to 400mA.

VDD_3V3B Rail

The current supplied by the VDD_3V3A rail is not sufficient to power all of the 3.3V rails on the board. So a second LDO is supplied, U4, a TL5209A, which sources the VDD_3V3B rail. It is powered up just after the VDD_3V3A rail.

VDD_1V8 Rail

The VDD_1V8 rail can deliver up to 400mA and provides the power required for the 1.8V rails on the processor and the HDMI framer. This rail is not accessible for use anywhere else on the board.

VDD_CORE Rail

The VDD_CORE rail can deliver up to 1.2A at 1.1V. This rail is not accessible for use anywhere else on the board and connects only to the processor. This rail is fixed at 1.1V and should not be adjusted by SW using the PMIC. If you do, then the processor will no longer work.

VDD_MPU Rail

The VDD_MPU rail can deliver up to 1.2A. This rail is not accessible for use anywhere else on the board and connects only to the processor. This rail defaults to 1.1V and can be scaled up to allow for higher frequency operation. Changing of the voltage is set via the I2C interface from the processor.

VDDS_DDR Rail

The VDDS_DDR rail defaults to**1.5V** to support the DDR3L rails and can deliver up to 1.2A. It is possible to adjust this voltage rail down to 1.35V for lower power operation of the DDR3L device. Only DDR3L devices can support this voltage setting of 1.35V.

Power Sequencing

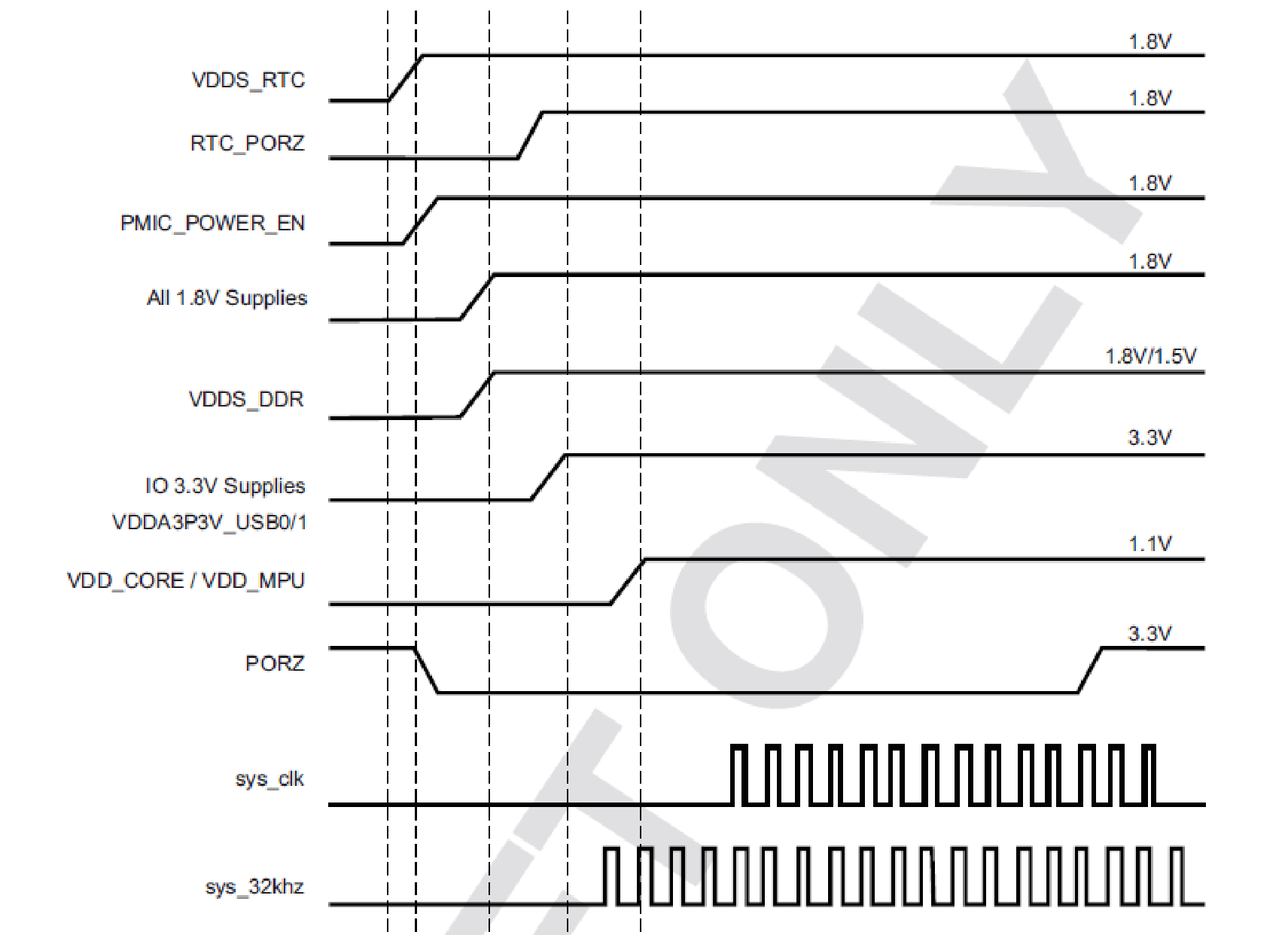

The power up process is consists of several stages and events. figure-26 describes the events that make up the power up process for the processor from the PMIC. This diagram is used elsewhere to convey additional information. I saw no need to bust it up into smaller diagrams. It is from the processor datasheet supplied by Texas Instruments.

Fig. 444 Power Rail Power Up Sequencing#

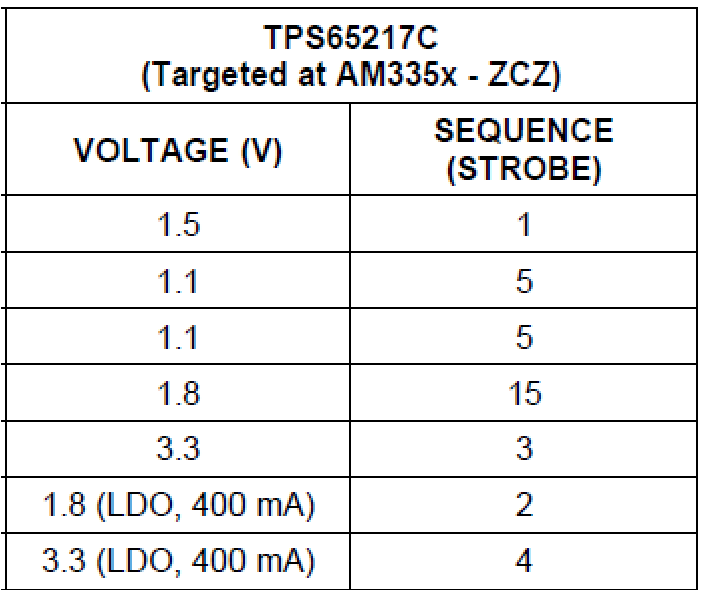

figure-27 the voltage rail sequencing for the TPS65217C as it powers up and the voltages on each rail. The power sequencing starts at 15 and then goes to one. That is the way the TPS65217C is configured. You can refer to the TPS65217C datasheet for more information.

Fig. 445 TPS65217C Power Sequencing Timing#

Power LED#

The power LED is a blue LED that will turn on once the TPS65217C has finished the power up procedure. If you ever see the LED flash once, that means that the**TPS65217C** started the process and encountered an issue that caused it to shut down. The connection of the LED is shown in figure-25.

TPS65217C Power Up Process#

Figure below shows the interface between the TPS65217C and the processor. It is a cut from the PDF form of the schematic and reflects what is on the schematic.

Fig. 446 Power Processor Interfaces#

When voltage is applied, DC or USB, the TPS65217C connects the power to the SYS output pin which drives the switchers and LDOs in the TPS65217C.

At power up all switchers and LDOs are off except for the VRTC LDO (1.8V), which provides power to the VRTC rail and controls the RTC_PORZn input pin to the processor, which starts the power up process of the processor. Once the RTC rail powers up, the RTC_PORZn pin, driven by the LDO_PGOOD signal from the TPS65217C, of the processor is released.

Once the RTC_PORZn reset is released, the processor starts the initialization process. After the RTC stabilizes, the processor launches the rest of the power up process by activating the PMIC_POWER_EN signal that is connected to the TPS65217C which starts the TPS65217C power up process.

The LDO_PGOOD signal is provided by the**TPS65217C** to the processor. As this signal is 1.8V from the TPS65217C by virtue of the TPS65217C VIO rail being set to 1.8V, and the RTC_PORZ signal on the processor is 3.3V, a voltage level shifter, U4, is used. Once the LDOs and switchers are up on the TPS65217C, this signal goes active releasing the processor. The LDOs on the TPS65217C are used to power the VRTC rail on the processor.

Processor Control Interface#

figure-28 above shows two interfaces between the processor and the TPS65217C used for control after the power up sequence has completed.

The first is the I2C0 bus. This allows the processor to turn on and off rails and to set the voltage levels of each regulator to supports such things as voltage scaling.

The second is the interrupt signal. This allows the TPS65217C to alert the processor when there is an event, such as when the power button is pressed. The interrupt is an open drain output which makes it easy to interface to 3.3V of the processor.

Low Power Mode Support#

This section covers three general power down modes that are available. These modes are only described from a Hardware perspective as it relates to the HW design.

RTC Only

In this mode all rails are turned off except the VDD_RTC. The processor will need to turn off all the rails to enter this mode. The VDD_RTC staying on will keep the RTC active and provide for the wakeup interfaces to be active to respond to a wake up event.

RTC Plus DDR

In this mode all rails are turned off except the VDD_RTC and the VDDS_DDR, which powers the DDR3L memory. The processor will need to turn off all the rails to enter this mode. The VDD_RTC staying on will keep the RTC active and provide for the wakeup interfaces to be active to respond to a wake up event.

The VDDS_DDR rail to the DDR3L is provided by the 1.5V rail of the TPS65217C and with VDDS_DDR active, the DDR3L can be placed in a self refresh mode by the processor prior to power down which allows the memory data to be saved.

Currently, this feature is not included in the standard software release. The plan is to include it in future releases.

Voltage Scaling

For a mode where the lowest power is possible without going to sleep, this mode allows the voltage on the ARM processor to be lowered along with slowing the processor frequency down. The I2C0 bus is used to control the voltage scaling function in the TPS65217C.

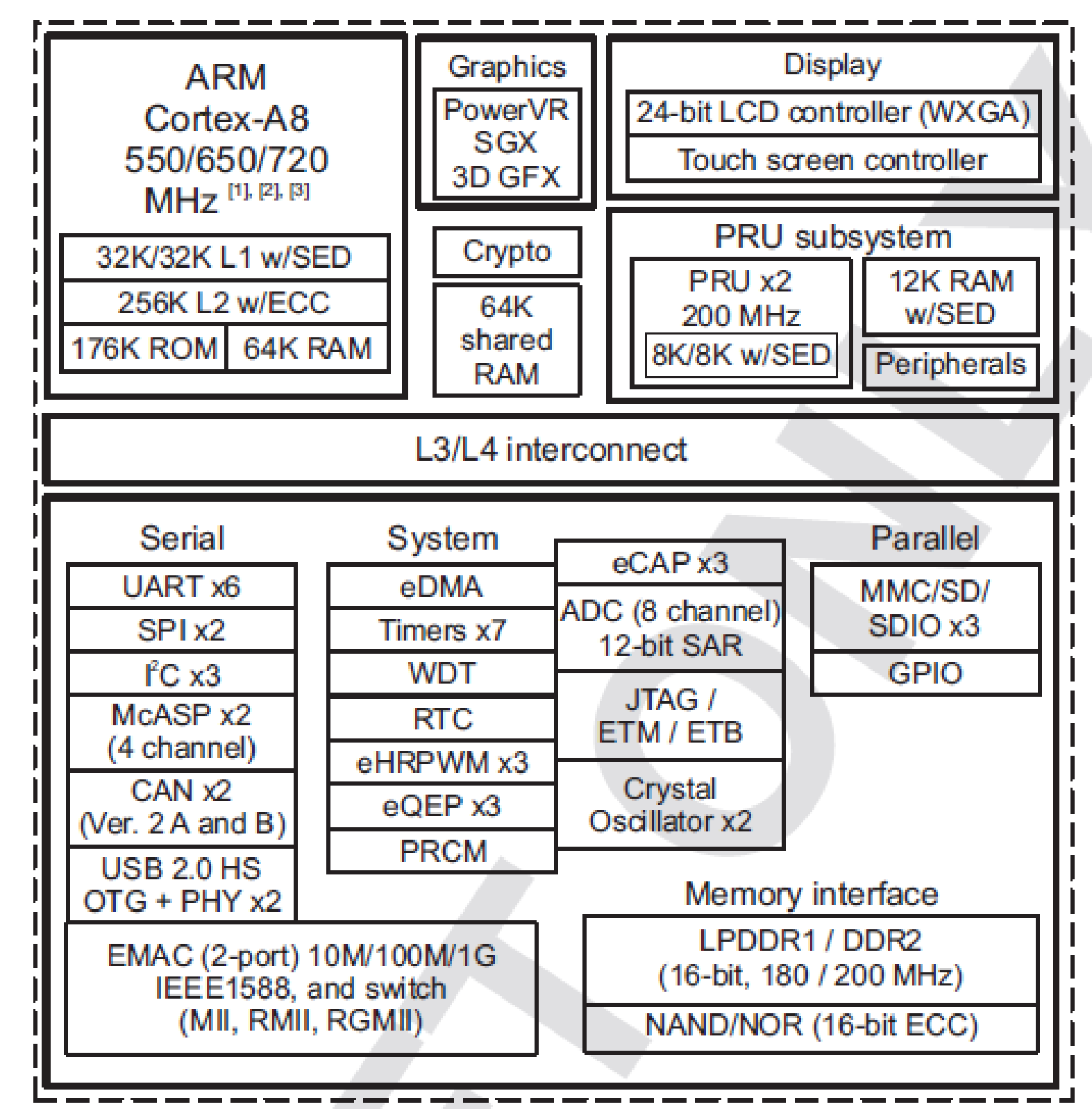

Sitara AM3358BZCZ100 Processor#

The board is designed to use the Sitara AM3358BZCZ100 processor in the 15 x 15 package. Earlier revisions of the board used the XM3359AZCZ100 processor.

Description#

Figure below shows is a high level block diagram of the processor. For more information on the processor, go to http://www.ti.com/product/am3358

Fig. 447 Sitara AM3358BZCZ Block Diagram#

High Level Features#

Operating Systems |

Linux, Android, Windows Embedded CE,QNX,ThreadX |

MMC/SD |

3 |

|---|---|---|---|

Standby Power |

7 mW |

CAN |

2 |

ARM CPU |

1 ARM Cortex-A8 |

UART (SCI) |

6 |

ARM MHz (Max.) |

275,500,600,800,1000 |

ADC |

8-ch 12-bit |

ARM MIPS (Max.) |

1000,1200,2000 |

PWM (Ch) |

3 |

Graphics Acceleration |

1 3D |

eCAP |

3 |

Other Hardware Acceleration |

2 PRU-ICSS,Crypto Accelerator |

eQEP |

3 |

On-Chip L1 Cache |

64 KB (ARM Cortex-A8) |

RTC |

1 |

On-Chip L2 Cache |

256 KB (ARM Cortex- A8) |

I2C |

3 |

Other On-Chip Memory |

128 KB |

McASP |

2 |

Display Options |

LCD |

SPI |

2 |

General Purpose Memory |

1 16-bit (GPMC, NAND flash, NOR Flash, SRAM) |

DMA (Ch) |

64-Ch EDMA |

DRAM |

1 16-bit (LPDDR-400,DDR2-532, DDR3-400) |

IO Supply (V) |

1.8V(ADC), 3.3V |

USB Ports |

2 |

Operating Temperature Range (C) |

40 to 90 |

Documentation#

Full documentation for the processor can be found on the TI website at http://www.ti.com/product/am3358 for the current processor used on the board. Make sure that you always use the latest datasheets and Technical Reference Manuals (TRM).

Crystal Circuitry#

Fig. 448 Processor Crystals#

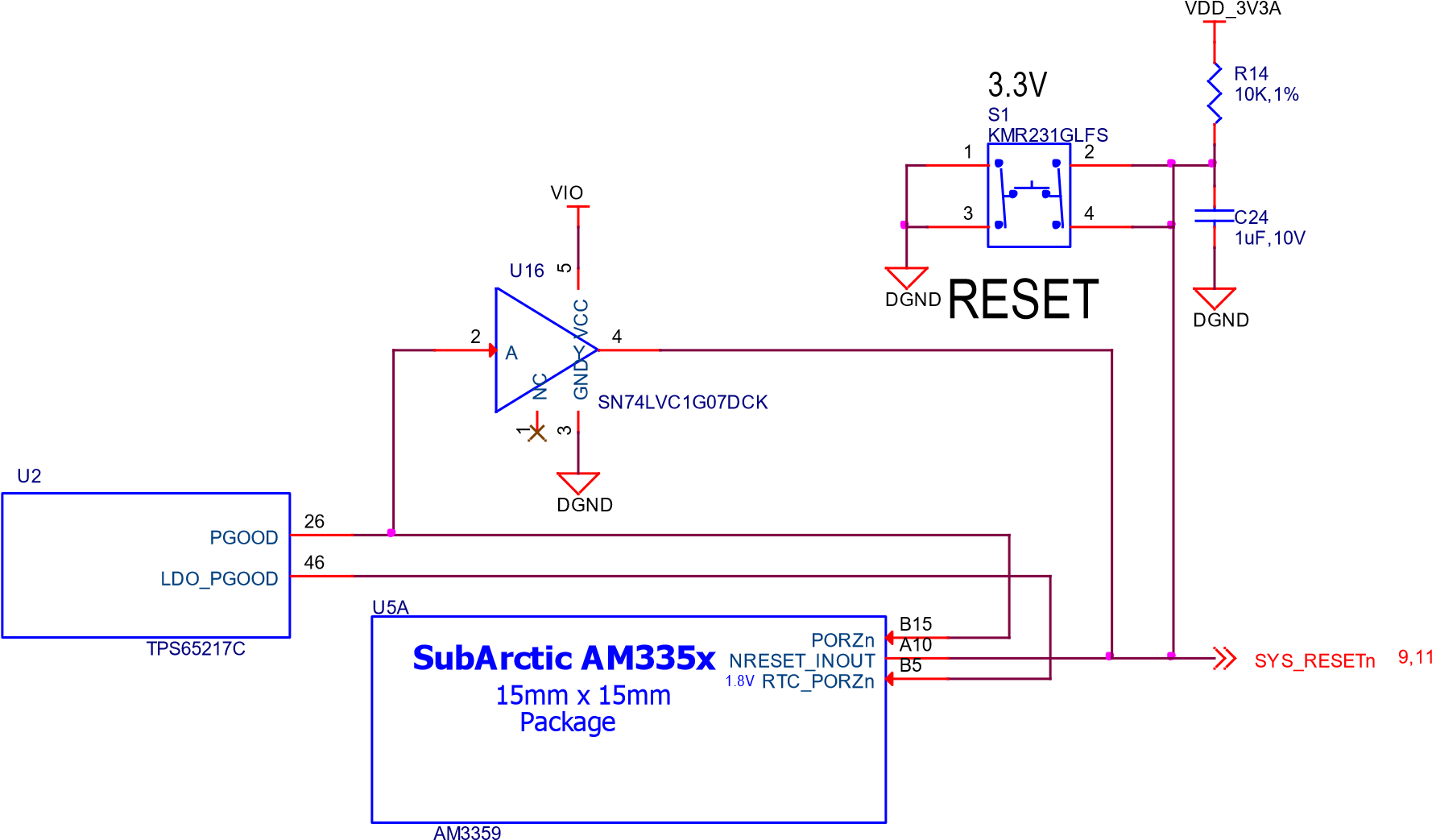

Reset Circuitry#

figure-31 is the board reset circuitry. The initial power on reset is generated by the TPS65217C power management IC. It also handles the reset for the Real Time Clock.

The board reset is the SYS_RESETn signal. This is connected to the NRESET_INOUT pin of the processor. This pin can act as an input or an output. When the reset button is pressed, it sends a warm reset to the processor and to the system.

On the revision A5D board, a change was made. On power up, the NRESET_INOUT signal can act as an output. In this instance it can cause the SYS_RESETn line to go high prematurely. In order to prevent this, the PORZn signal from the TPS65217C is connected to the SYS_RESETn line using an open drain buffer. These ensure that the line does not momentarily go high on power up.

Fig. 449 Board Reset Circuitry#

This change is also in all revisions after A5D.

DDR3L Memory

The BeagleBone Black uses a single MT41K256M16HA-125 512MB DDR3L device from Micron that interfaces to the processor over 16 data lines, 16 address lines, and 14 control lines. On rev C we added the Kingston KE4CN2H5A-A58 device as a source for the DDR3L device**.**

The following sections provide more details on the design.

Memory Device#

The design supports the standard DDR3 and DDR3L x16 devices and is built using the DDR3L. A single x16 device is used on the board and there is no support for two x8 devices. The DDR3 devices work at 1.5V and the DDR3L devices can work down to

1.35V to achieve lower power. The DDR3L comes in a 96-BALL FBGA package with 0.8 mil pitch. Other standard DDR3 devices can also be supported, but the DDR3L is the lower power device and was chosen for its ability to work at 1.5V or 1.35V. The standard frequency that the DDR3L is run at on the board is 400MHZ.

DDR3L Memory Design#

figure-32 is the schematic for the DDR3L memory device. Each of the groups of signals is described in the following lines.

Address Lines: Provide the row address for ACTIVATE commands, and the column address and auto pre-charge bit (A10) for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one bank (A10 LOW, bank selected by BA[2:0]) or all banks (A10 HIGH). The address inputs also provide the op-code during a LOAD MODE command. Address inputs are referenced to VREFCA. A12/BC#: When enabled in the mode register (MR), A12 is sampled during READ and WRITE commands to determine whether burst chop (on-the-fly) will be performed (HIGH = BL8 or no burst chop, LOW = BC4 burst chop).

Bank Address Lines: BA[2:0] define the bank to which an ACTIVATE, READ, WRITE, or PRECHARGE command is being applied. BA[2:0] define which mode register (MR0, MR1, MR2, or MR3) is loaded during the LOAD MODE command. BA[2:0] are referenced to VREFCA.

CK and CK# Lines: are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and the negative edge of CK#. Output data strobe (DQS, DQS#) is referenced to the crossings of CK and CK#.

Clock Enable Line: CKE enables (registered HIGH) and disables (registered LOW) internal circuitry and clocks on the DRAM. The specific circuitry that is enabled/disabled is dependent upon the DDR3 SDRAM configuration and operating mode. Taking CKE LOW provides PRECHARGE power-down and SELF REFRESH operations (all banks idle) or active power-down (row active in any bank). CKE is synchronous for powerdown entry and exit and for self refresh entry. CKE is asynchronous for self refresh exit. Input buffers (excluding CK, CK#, CKE, RESET#, and ODT) are disabled during powerdown. Input buffers (excluding CKE and RESET#) are disabled during SELF REFRESH. CKE is referenced to VREFCA.

Fig. 450 DDR3L Memory Design#

Chip Select Line: CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when CS# is registered HIGH. CS# provides for external rank selection on systems with multiple ranks. CS# is considered part of the command code. CS# is referenced to VREFCA.

Input Data Mask Line: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with the input data during a write access. Although the DM ball is input-only, the DM loading is designed to match that of the DQ and DQS balls. DM is referenced to VREFDQ.

On-die Termination Line: ODT enables (registered HIGH) and disables (registered LOW) termination resistance internal to the DDR3L SDRAM. When enabled in normal operation, ODT is only applied to each of the following balls: DQ[7:0], DQS, DQS#, and DM for the x8; DQ[3:0], DQS, DQS#, and DM for the x4. The ODT input is ignored if disabled via the LOAD MODE command. ODT is referenced to VREFCA.

Power Rails#

The DDR3L memory device and the DDR3 rails on the processor are supplied by the**TPS65217C**. Default voltage is 1.5V but can be scaled down to 1.35V if desired.

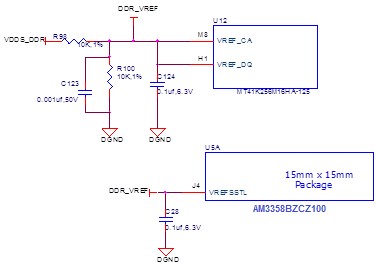

VREF#

The VREF signal is generated from a voltage divider on the**VDDS_DDR** rail that powers the processor DDR rail and the DDR3L device itself. Figure 33 below shows the configuration of this signal and the connection to the DDR3L memory device and the processor.

Fig. 451 DDR3L VREF Design#

4GB eMMC Memory#

The eMMC is a communication and mass data storage device that includes a Multi-MediaCard (MMC) interface, a NAND Flash component, and a controller on an advanced 11-signal bus, which is compliant with the MMC system specification. The nonvolatile eMMC draws no power to maintain stored data, delivers high performance across a wide range of operating temperatures, and resists shock and vibration disruption.

One of the issues faced with SD cards is that across the different brands and even within the same brand, performance can vary. Cards use different controllers and different memories, all of which can have bad locations that the controller handles. But the controllers may be optimized for reads or writes. You never know what you will be getting. This can lead to varying rates of performance. The eMMC card is a known controller and when coupled with the 8bit mode, 8 bits of data instead of 4, you get double the performance which should result in quicker boot times.

The following sections describe the design and device that is used on the board to implement this interface.

eMMC Device#

The device used is one of two different devices:

Micron MTFC4GLDEA 0M WT

Kingston KE4CN2H5A-A58

The package is a 153 ball WFBGA device on both devices.

eMMC Circuit Design#

figure-34 is the design of the eMMC circuitry. The eMMC device is connected to the MMC1 port on the processor. MMC0 is still used for the microSD card as is currently done on the original BeagleBone. The size of the eMMC supplied is now 4GB.

The device runs at 3.3V both internally and the external I/O rails. The VCCI is an internal voltage rail to the device. The manufacturer recommends that a 1uF capacitor be attached to this rail, but a 2.2uF was chosen to provide a little margin.

Pullup resistors are used to increase the rise time on the signals to compensate for any capacitance on the board.

Fig. 452 eMMC Memory Design#

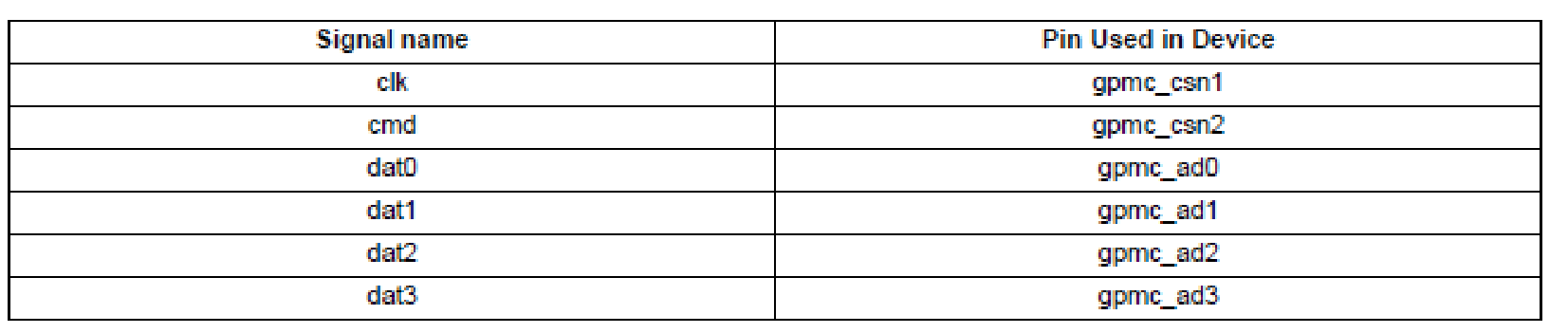

The pins used by the eMMC1 in the boot mode are listed below in Table 6.

Fig. 453 eMMC Boot Pins#

For eMMC devices the ROM will only support raw mode. The ROM Code reads out raw sectors from image or the booting file within the file system and boots from it. In raw mode the booting image can be located at one of the four consecutive locations in the main area: offset 0x0 / 0x20000 (128 KB) / 0x40000 (256 KB) / 0x60000 (384 KB). For this reason, a booting image shall not exceed 128KB in size. However it is possible to flash a device with an image greater than 128KB starting at one of the aforementioned locations. Therefore the ROM Code does not check the image size. The only drawback is that the image will cross the subsequent image boundary. The raw mode is detected by reading sectors #0, #256, #512, #768. The content of these sectors is then verified for presence of a TOC structure. In the case of a GP Device, a Configuration Header (CH)*must* be located in the first sector followed by a GP header. The CH might be void (only containing a CHSETTINGS item for which the Valid field is zero).

The ROM only supports the 4-bit mode. After the initial boot, the switch can be made to 8-bit mode for increasing the overall performance of the eMMC interface.

Board ID EEPROM#

The BeagleBone is equipped with a single 32Kbit(4KB) 24LC32AT-I/OT EEPROM to allow the SW to identify the board. Table 7 below defined the contents of the EEPROM.

Name |

Size (bytes) |

Contents |

|---|---|---|

Header |

4 |

0xAA, 0x55, 0x33, EE |

Board Name |

8 |

Name for board in ASCII: A335BNLT |

Version |

4 |

Hardware version code for board in ASCII: 00A3 for Rev A3, 00A4 for Rev A4, 00A5 for Rev A5, 00A6 for Rev A6,00B0 for Rev B, and 00C0 for Rev C. |

Serial Number |

12 |

Serial number of the board. This is a 12 character string which is: WWYY4P16nnnn where, WW = 2 digit week of the year of production YY = 2 digit year of production BBBK = BeagleBone Black nnnn = incrementing board number |

Configuration Option |

32 |

Codes to show the configuration setup on this board. All FF |

RSVD |

6 |

FF FF FF FF FF FF |

RSVD |

6 |

FF FF FF FF FF FF |

RSVD |

6 |

FF FF FF FF FF FF |

Available |

4018 |

Available space for other non-volatile codes/data |

Fig. 454 EEPROM Design Rev A5#

The EEPROM is accessed by the processor using the I2C 0 bus. The WP pin is enabled by default. By grounding the test point, the write protection is removed.

The first 48 locations should not be written to if you choose to use the extras storage space in the EEPROM for other purposes. If you do, it could prevent the board from booting properly as the SW uses this information to determine how to set up the board.

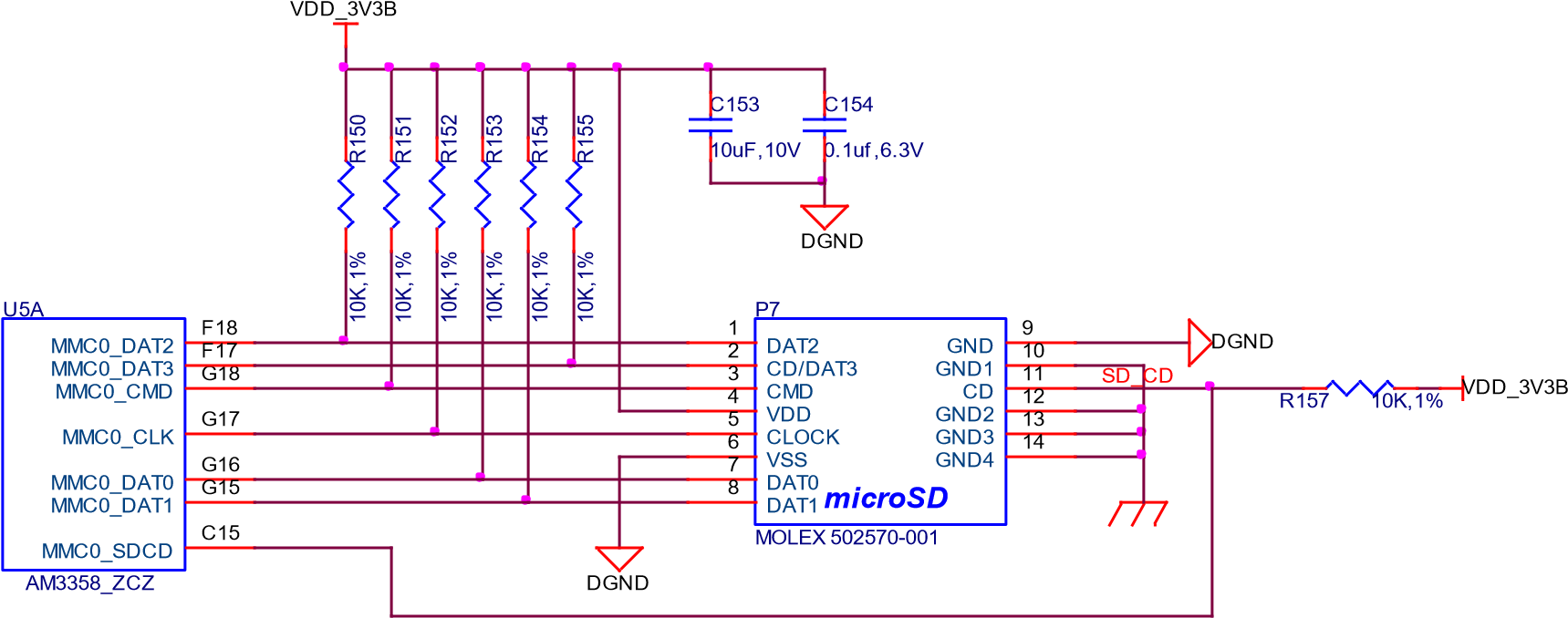

Micro Secure Digital#

The microSD connector on the board will support a microSD card that can be used for booting or file storage on the BeagleBone Black.

microSD Design#

Fig. 455 microSD Design#

The signals MMC0-3 are the data lines for the transfer of data between the processor and the microSD connector.

The MMC0_CLK signal clocks the data in and out of the microSD card.

The MMCO_CMD signal indicates that a command versus data is being sent.

There is no separate card detect pin in the microSD specification. It uses MMCO_DAT3 for that function. However, most microSD connectors still supply a CD function on the connectors. In the BeagleBone Black design, this pin is connected to the MMC0_SDCD pin for use by the processor. You can also change the pin to GPIO0_6, which is able to wake up the processor from a sleep mode when an microSD card is inserted into the connector.

Pullup resistors are provided on the signals to increase the rise times of the signals to overcome PCB capacitance.

Power is provided from the VDD_3V3B rail and a 10uF capacitor is provided for filtering.

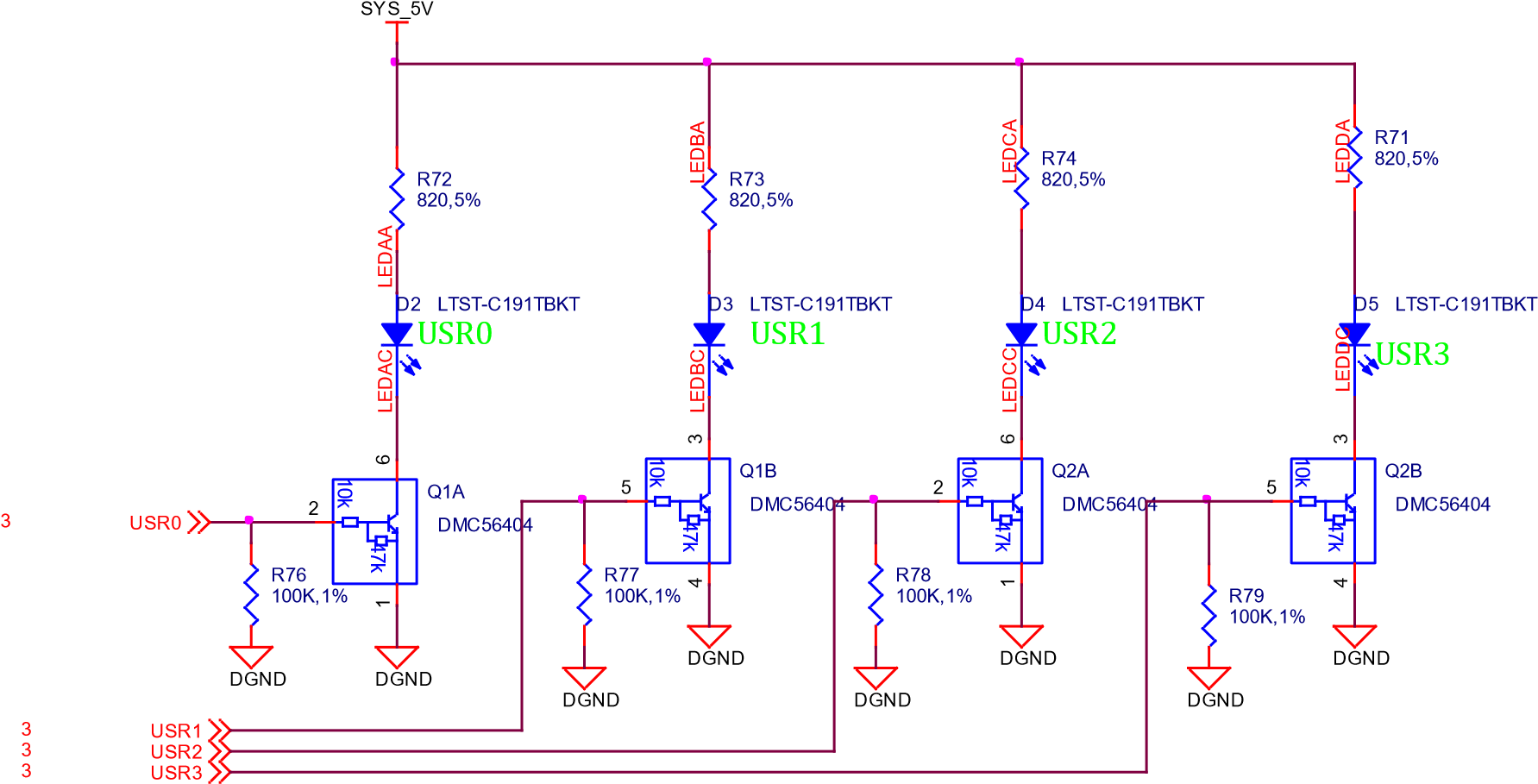

6.6 User LEDs#

There are four user LEDs on the BeagleBone Black. These are connected to GPIO pins on the processor. Figure 37 shows the interfaces for the user LEDs.

Fig. 456 User LEDs#

Resistors R71-R74 were changed to 4.75K on the revision A5B and later boards.

LED |

GPIO SIGNAL |

PROC PIN |

|---|---|---|

USR0 |

GPIO1_21 |

V15 |

USR1 |

GPIO1_22 |

U15 |

USR2 |

GPIO1_23 |

T15 |

USR3 |

GPIO1_24 |

V16 |

A logic level of “1” will cause the LEDs to turn on.

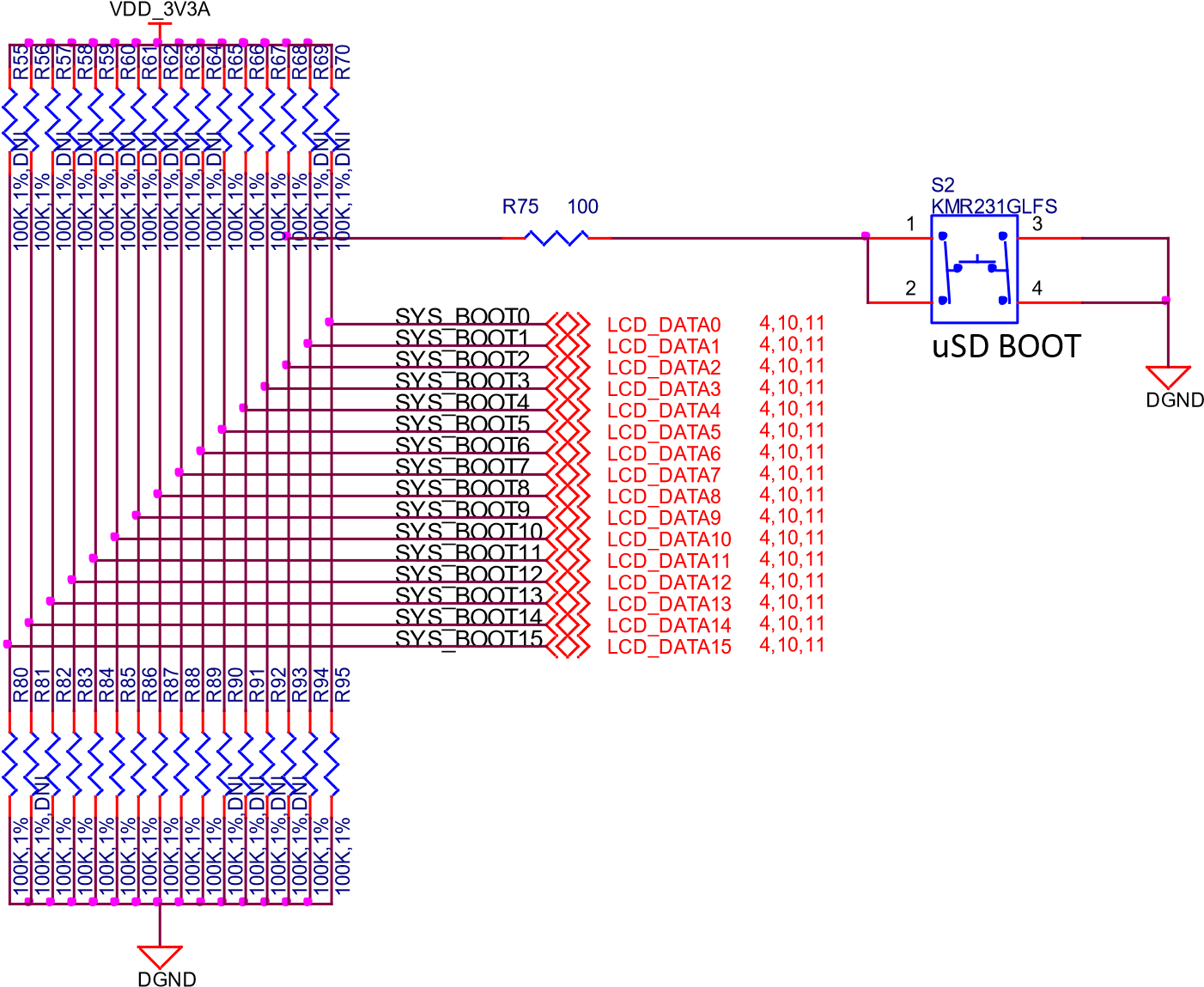

Boot Configuration#

The design supports two groups of boot options on the board. The user can switch between these modes via the Boot button. The primary boot source is the onboard eMMC device. By holding the Boot button, the user can force the board to boot from the microSD slot. This enables the eMMC to be overwritten when needed or to just boot an alternate image. The following sections describe how the boot configuration works.

In most applications, including those that use the provided demo distributions available from beagleboard.org the processor-external boot code is composed of two stages. After the primary boot code in the processor ROM passes control, a secondary stage (secondary program loader – “SPL” or “MLO”) takes over. The SPL stage initializes only the required devices to continue the boot process, and then control is transferred to the third stage “U-boot”. Based on the settings of the boot pins, the ROM knows where to go and get the SPL and UBoot code. In the case of the BeagleBone Black, that is either eMMC or microSD based on the position of the boot switch.

Boot Configuration Design#

figure-38 shows the circuitry that is involved in the boot configuration process. On power up, these pins are read by the processor to determine the boot order. S2 is used to change the level of one bit from HI to LO which changes the boot order.

Fig. 457 Processor Boot Configuration Design#

It is possible to override these setting via the expansion headers. But be careful not to add too much load such that it could interfere with the operation of the HDMI interface or LCD panels. If you choose to override these settings, it is strongly recommended that you gate these signals with the SYS_RESETn signal. This ensures that after coming out of reset these signals are removed from the expansion pins.

Default Boot Options#

Based on the selected option found in figure-39 below, each of the boot sequences for each of the two settings is shown.

Fig. 458 Processor Boot Configuration#

The first row in <<figure-39>> is the default setting. On boot, the processor will look for the eMMC on the MMC1 port first, followed by the microSD slot on MMC0, USB0 and UART0. In the event there is no microSD card and the eMMC is empty, UART0 or USB0 could be used as the board source.

If you have a microSD card from which you need to boot from, hold the boot button down. On boot, the processor will look for the SPIO0 port first, then microSD on the MMC0 port, followed by USB0 and UART0. In the event there is no microSD card and the eMMC is empty, USB0 or UART0 could be used as the board source.

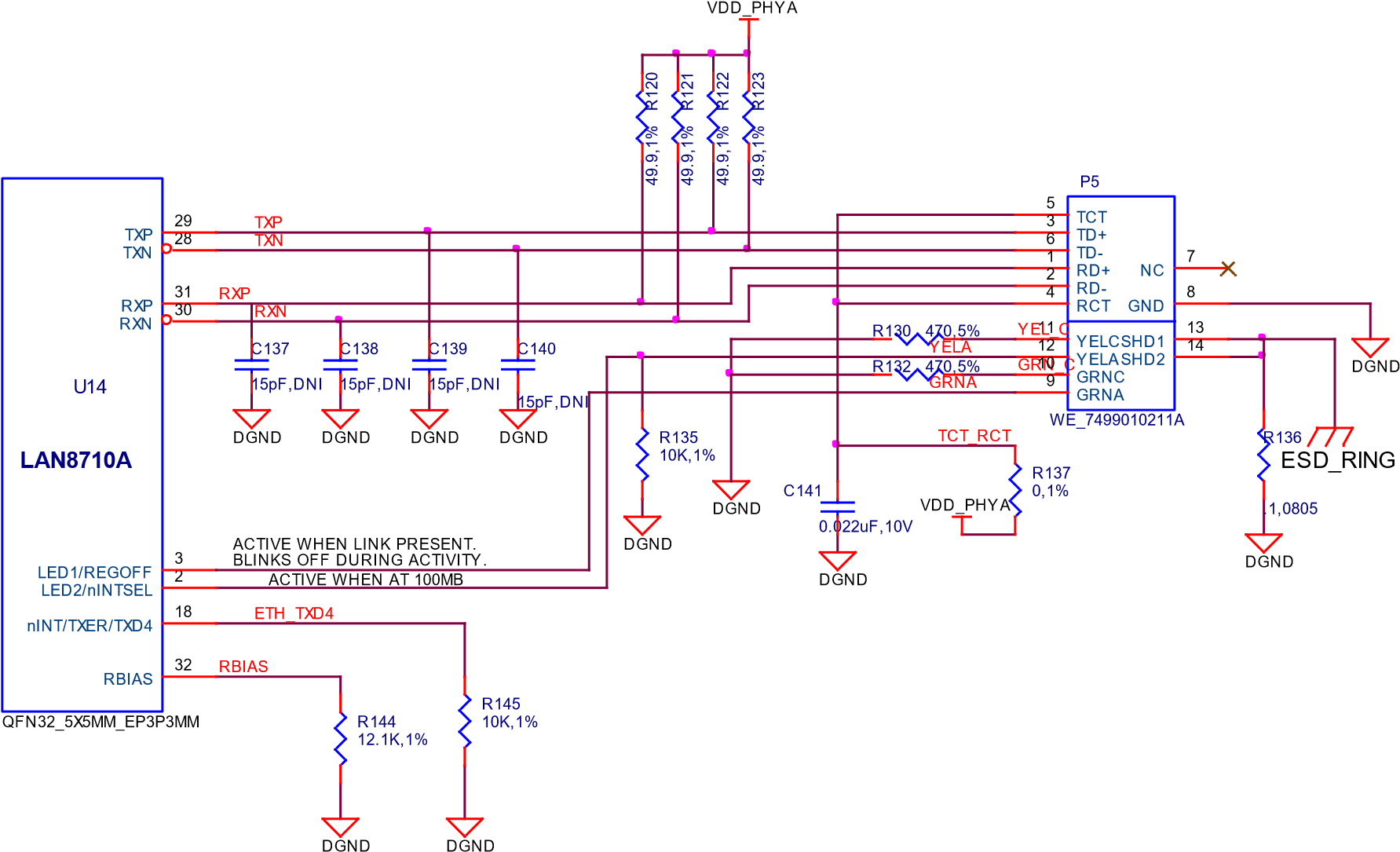

10/100 Ethernet#

The BeagleBone Black is equipped with a 10/100 Ethernet interface. It uses the same PHY as is used on the original BeagleBone. The design is described in the following sections.

Ethernet Processor Interface#

Fig. 459 Ethernet Processor Interface#

This is the same interface as is used on the BeagleBone. No changes were made in this design for the board.

Ethernet Connector Interface#

The off board side of the PHY connections are shown in Figure 41 below.

Fig. 460 Ethernet Connector Interface#

This is the same interface as is used on the BeagleBone. No changes were made in this design for the board.

Ethernet PHY Power, Reset, and Clocks#

Fig. 461 Ethernet PHY, Power, Reset, and Clocks#

VDD_3V3B Rail

The VDD_3V3B rail is the main power rail for the LAN8710A. It originates at the VD_3V3B regulator and is the primary rail that supports all of the peripherals on the board. This rail also supplies the VDDIO rails which set the voltage levels for all of the I/O signals between the processor and the**LAN8710A**.

VDD_PHYA Rail

A filtered version of VDD_3V3B rail is connected to the VDD rails of the LAN8710 and the termination resistors on the Ethernet signals. It is labeled as VDD_PHYA. The filtering inductor helps block transients that may be seen on the VDD_3V3B rail.

PHY_VDDCR Rail

The PHY_VDDCR rail originates inside the LAN8710A. Filter and bypass capacitors are used to filter the rail. Only circuitry inside the LAN8710A uses this rail.

SYS_RESET

The reset of the LAN8710A is controlled via the SYS_RESETn signal, the main board reset line.

Clock Signals

A crystal is used to create the clock for the LAN8710A. The processor uses the RMII_RXCLK signal to provide the clocking for the data between the processor and the LAN8710A.

LAN8710A Mode Pins#

There are mode pins on the LAN8710A that sets the operational mode for the PHY when coming out of reset. These signals are also used to communicate between the processor and the LAN8710A. As a result, these signals can be driven by the processor which can cause the PHY not to be initialized correctly. To ensure that this does not happen, three low value pull up resistors are used. Figure 43 below shows the three mode pin resistors.

Fig. 462 Ethernet PHY Mode Pins#

This will set the mode to be 111, which enables all modes and enables auto-negotiation.

HDMI Interface#

The BeagleBone Black has an onboard HDMI framer that converts the LCD signals and audio signals to drive a HDMI monitor. The design uses an NXP TDA19988 HDMI Framer.

The following sections provide more detail into the design of this interface.

Supported Resolutions#

The maximum resolution supported by the BeagleBone Black is 1280x1024 @ 60Hz. Table 9 below shows the supported resolutions. Not all resolutions may work on all monitors, but these have been tested and shown to work on at least one monitor. EDID is supported on the BeagleBone Black. Based on the EDID reading from the connected monitor, the highest compatible resolution is selected.

RESOLUTION |

AUDIO |

|---|---|

800 x 600 @60Hz |

|

800 x 600 @56Hz |

|

640 x 480 @75Hz |

|

640 x 480 @60Hz |

YES |

720 x 400 @70Hz |

|

1280 x 1024 @75Hz |

|

1024 x 768 @75Hz |

|

1024 x 768 @70Hz |

|

1024 x 768 @60Hz |

|

800 x 600 @75Hz |

|

800 x 600 @72Hz |

|

720 x 480 @60Hz |

YES |

1280 x 720 @60Hz |

YES |

1920 x 1080 @24Hz |

YES |

NOTE: The updated software image used on the Rev A5B and later boards added support for 1920x1080@24HZ.

Audio is limited to CEA supported resolutions. LCD panels only activate the audio in CEA modes. This is a function of the specification and is not something that can be fixed on the board via a hardware change or a software change.

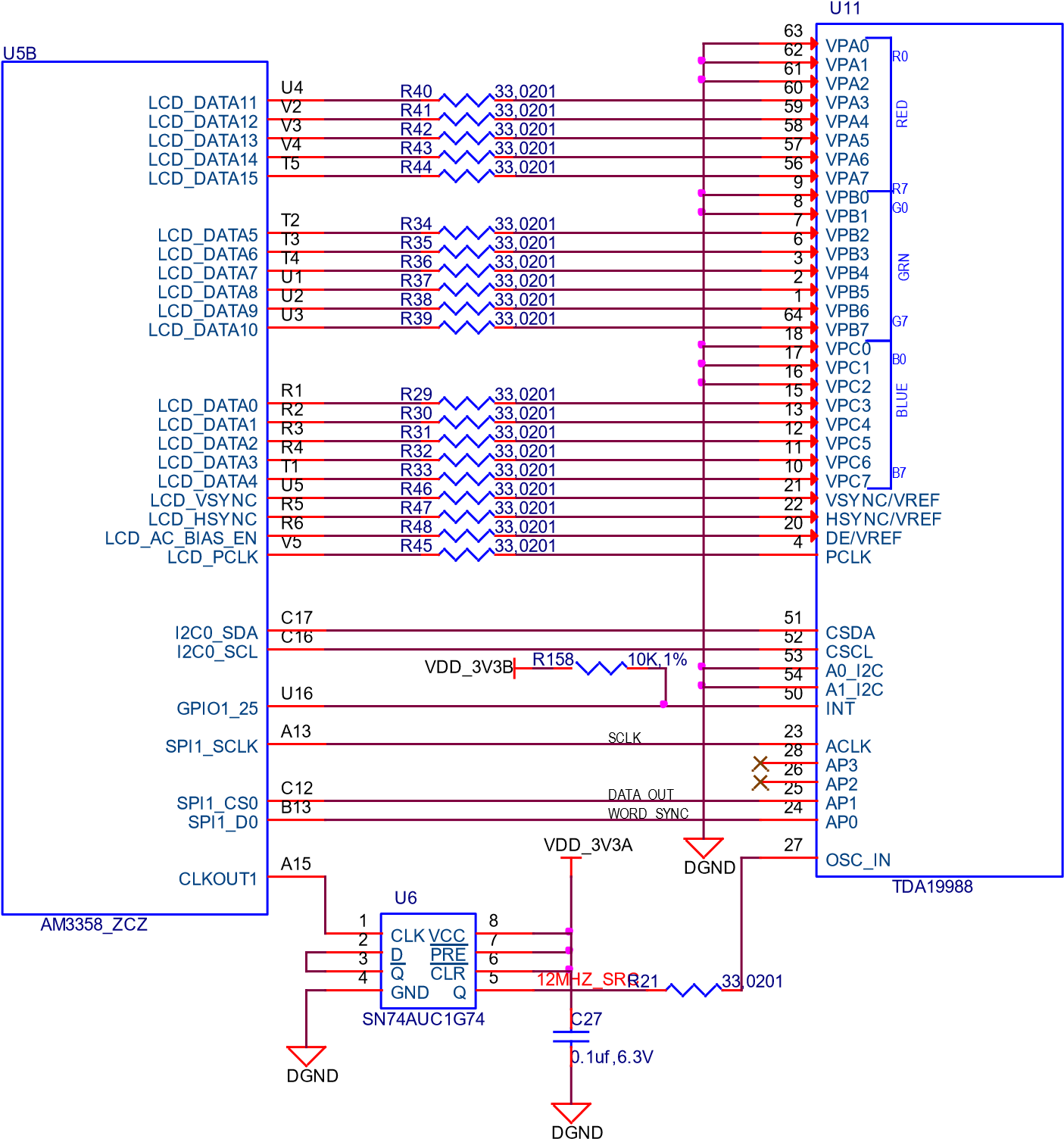

HDMI Framer#

The TDA19988 is a High-Definition Multimedia Interface (HDMI) 1.4a transmitter. It is backward compatible with DVI 1.0 and can be connected to any DVI 1.0 or HDMI sink. The HDCP mode is not used in the design. The non-HDCP version of the device is used in the BeagleBone Black design.

This device provides additional embedded features like CEC (Consumer Electronic Control). CEC is a single bidirectional bus that transmits CEC over the home appliance network connected through this bus. This eliminates the need of any additional device to handle this feature. While this feature is supported in this device, as of this point, the SW to support this feature has not been implemented and is not a feature that is considered critical. It can be switched to very low power Standby or Sleep modes to save power when HDMI is not used. TDA19988 embeds I~2~C-bus master interface for DDC-bus communication to read EDID. This device can be controlled or configured via I~2~C-bus interface.

HDMI Video Processor Interface#

The Figure 44 shows the connections between the processor and the HDMI framer device. There are 16 bits of display data, 5-6-5 that is used to drive the framer. The reason for 16 bits is that allows for compatibility with display and LCD capes already available on the original BeagleBone. The unused bits on the TDA19988 are tied low. In addition to the data signals are the VSYNC, HSYNC, DE, and PCLK signals that round out the video interface from the processor.

Fig. 463 HDMI Framer Processor Interface#

HDMI Control Processor Interface#

In order to use the TDA19988, the processor needs to setup the device. This is done via the I2C interface between the processor and the TDA19988. There are two signals on the TDA19988 that could be used to set the address of the TDA19988. In this design they are both tied low. The I2C interface supports both 400kHz and 100KhZ operation. Table 10 shows the I2C address.

Fig. 464 TDA19988 I2C Address#

Interrupt Signal#

There is a HDMI_INT signal that connects from the TDA19988 to the processor. This signal can be used to alert the processor in a state change on the HDMI interface.

Audio Interface#

There is an I2S audio interface between the processor and the TDA19988. Stereo audio can be transported over the HDMI interface to an audio equipped display. In order to create the required clock frequencies, an external 24.576MHz oscillator,*Y4*, is used. From this clock, the processor generates the required clock frequencies for the TDA19988.

There are three signals used to pass data from the processor to the TDA19988. SCLK is the serial clock. SPI1_CS0 is the data pin to the TDA199888. SPI1_D0 is the word sync pin. These signals are configured as I2S interfaces.

Audio is limited to CEA supported resolutions. LCD panels only activate the audio in CEA modes. This is a function of the specification and is not something that can be fixed on the board via a hardware change or a software change.

In order to create the correct clock frequencies, we had to add an external 24.576MHz oscillator. Unfortunately this had to be input into the processor using the pin previously used for GPIO3_21. In order to keep GPIO3_21 functionality, we provided a way to disable the oscillator if the need was there to use the pin on the expansion header. Figure 45 shows the oscillator circuitry.

Fig. 465 24.576MHZ Oscillator#

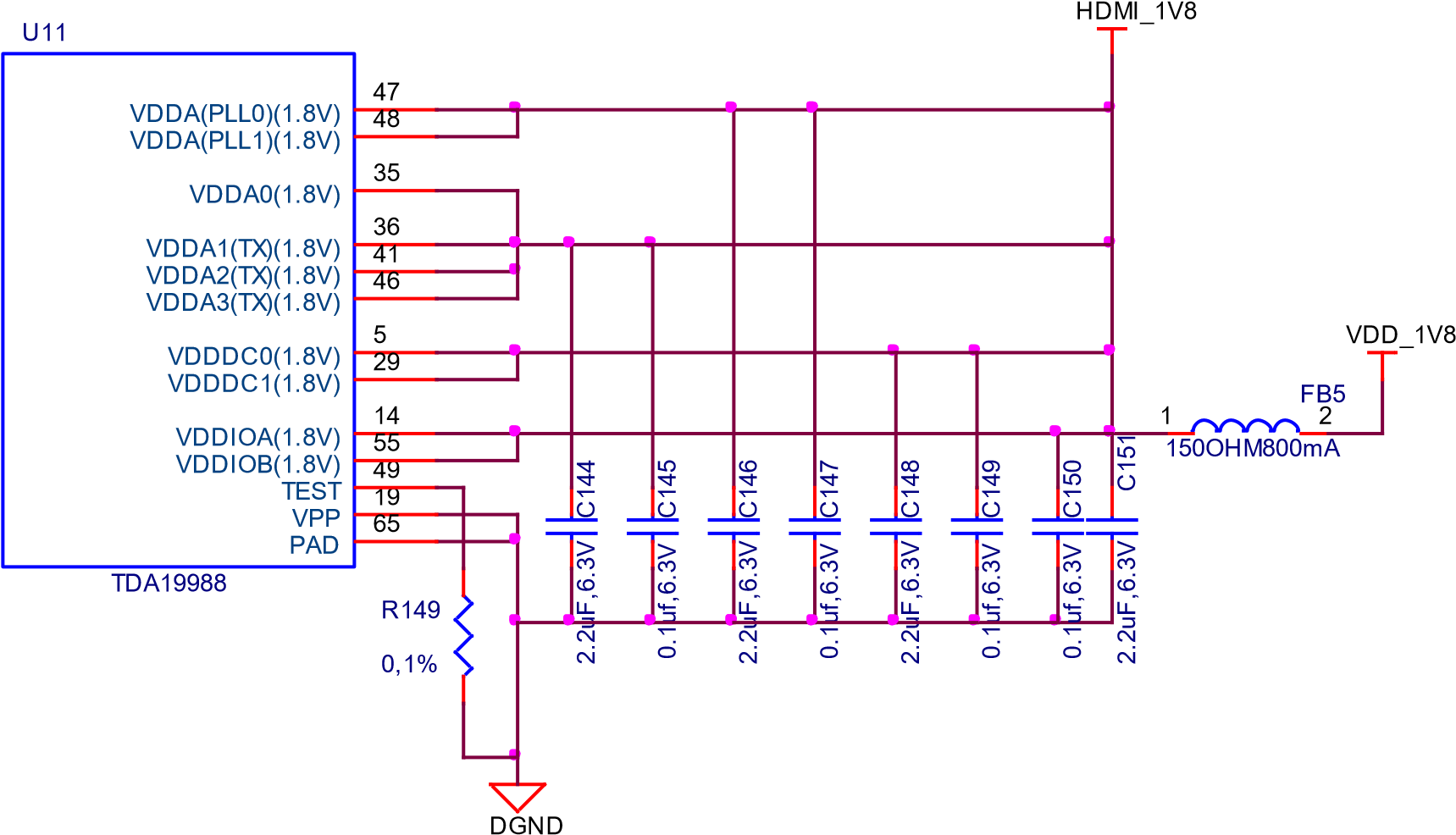

Power Connections#

figure-46 shows the power connections to the TDA19988 device. All voltage rails for the device are at 1.8V. A filter is provided to minimize any noise from the 1.8V rail getting back into the device.

Fig. 466 HDMI Power Connections#

All of the interfaces between the processor and the TDA19988 are 3.3V tolerant allowing for direct connection.

HDMI Connector Interface#

figure-47 shows the design of the interface between the HDMI Framer and the connector.

Fig. 467 Connector Interface Circuitry#

The connector for the HDMI interface is a microHDMI. It should be noted that this connector has a different pinout than the standard or mini HDMI connectors. D6 and D7 are ESD protection devices.

USB Host#

The board is equipped with a single USB host interface accessible from a single USB Type A female connector. <<figure-48>> is the design of the USB Host circuitry.

Fig. 468 USB Host circuit#

Power Switch#

U8 is a switch that allows the power to the connector to be turned on or off by the processor. It also has an over current detection that can alert the processor if the current gets too high via the**USB1_OC** signal. The power is controlled by the USB1_DRVBUS signal from the processor.

ESD Protection#

U9 is the ESD protection for the signals that go to the connector.

Filter Options#

FB7 and**FB8** were added to assist in passing the FCC emissions test. The USB1_VBUS signal is used by the processor to detect that the 5V is present on the connector. FB7 is populated and FB8 is replaced with a .1 ohm resistor.

PRU-ICSS#

The PRU-ICSS module is located inside the AM3358 processor. Access to these pins is provided by the expansion headers and is multiplexed with other functions on the board. Access is not provided to all of the available pins.

All documentation is located at http://github.com/beagleboard/am335x_pru_package_

This feature is not supported by Texas Instruments.

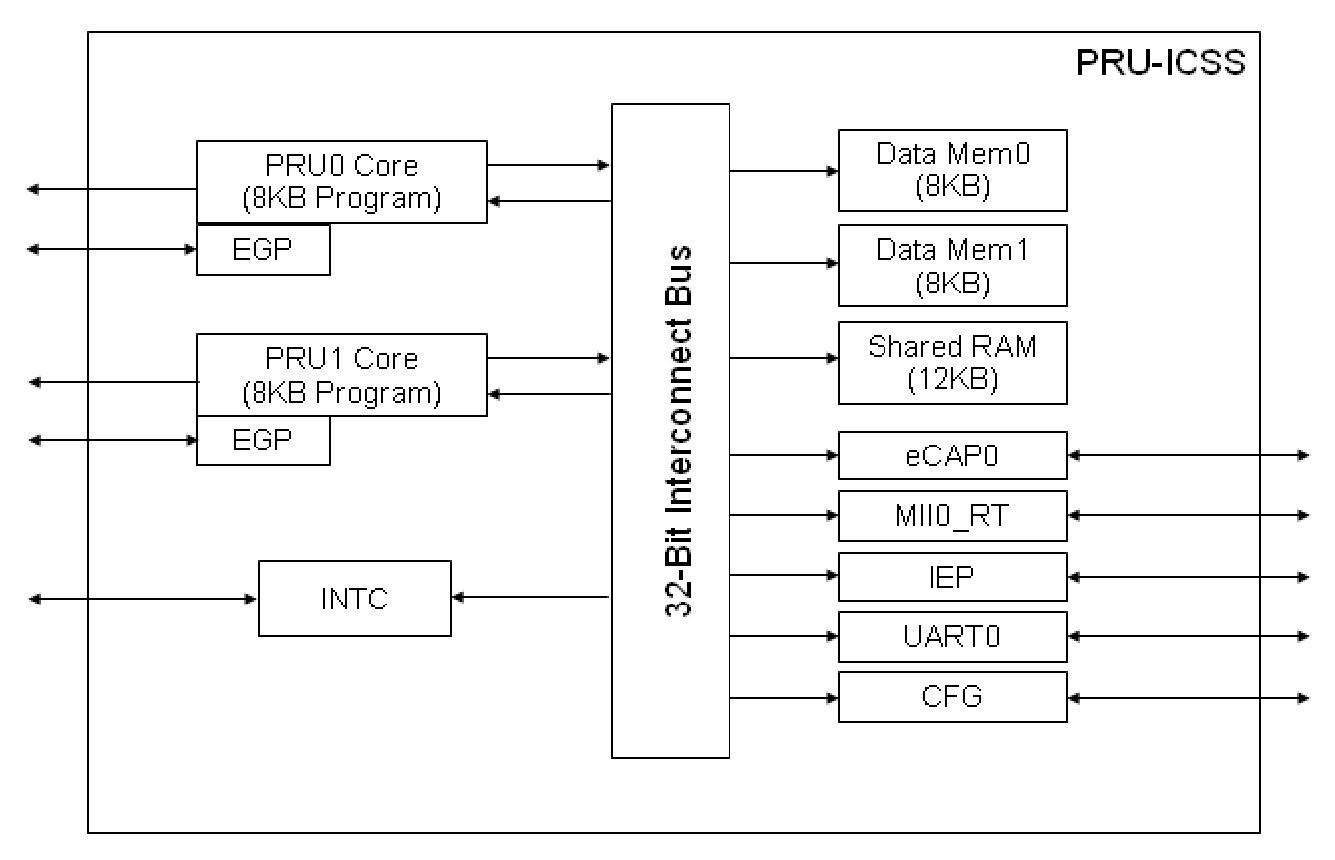

PRU-ICSS Features#

The features of the PRU-ICSS include:

Two independent programmable real-time (PRU) cores:

32-Bit Load/Store RISC architecture

8K Byte instruction RAM (2K instructions) per core

8K Bytes data RAM per core

12K Bytes shared RAM

Operating frequency of 200 MHz

PRU operation is little endian similar to ARM processor

All memories within PRU-ICSS support parity

Includes Interrupt Controller for system event handling

Fast I/O interface

16 input pins and 16 output pins per PRU core. (Not all of these are accessible on the BeagleBone Black).

PRU-ICSS Block Diagram#

Fig. 469 PRU-ICSS Block Diagram#

PRU-ICSS Pin Access#

Both PRU 0 and PRU1 are accessible from the expansion headers. Some may not be usable without first disabling functions on the board like LCD for example. Listed below is what ports can be accessed on each PRU.

8 outputs or 9 inputs

13 outputs or 14 inputs

UART0_TXD, UART0_RXD, UART0_CTS, UART0_RTS

PIN |

PROC |

NAME |

|||

|---|---|---|---|---|---|

11 |

R12 |

GPIO1_13 |

pr1_pru0_pru_r30_15 (Output) |

||

12 |

T12 |

GPIO1_12 |

pr1_pru0_pru_r30_14 (Output) |

||

15 |

U13 |

GPIO1_15 |

pr1_pru0_pru_r31_15 (Input) |

||

16 |

V13 |

GPIO1_14 |

pr1_pru0_pru_r31_14 (Input) |

||

20 |

V9 |

GPIO1_31 |

pr1_pru1_pru_r30_13 (Output) |

pr1_pru1_pru_r31_13 (INPUT) |

|

21 |

U9 |

GPIO1_30 |

pr1_pru1_pru_r30_12 (Output) |

pr1_pru1_pru_r31_12 (INPUT) |

|

27 |

U5 |

GPIO2_22 |

pr1_pru1_pru_r30_8 (Output) |

pr1_pru1_pru_r31_8 (INPUT) |

|

28 |

V5 |

GPIO2_24 |

pr1_pru1_pru_r30_10 (Output) |

pr1_pru1_pru_r31_10 (INPUT) |

|

29 |

R5 |

GPIO2_23 |

pr1_pru1_pru_r30_9 (Output) |

pr1_pru1_pru_r31_9 (INPUT) |

|

39 |

T3 |

GPIO2_12 |

pr1_pru1_pru_r30_6 (Output) |

pr1_pru1_pru_r31_6 (INPUT) |

|

40 |

T4 |

GPIO2_13 |

pr1_pru1_pru_r30_7 (Output) |

pr1_pru1_pru_r31_7 (INPUT) |

|

41 |

T1 |

GPIO2_10 |

pr1_pru1_pru_r30_4 (Output) |

pr1_pru1_pru_r31_4 (INPUT) |

|

42 |

T2 |

GPIO2_11 |

pr1_pru1_pru_r30_5 (Output) |

pr1_pru1_pru_r31_5 (INPUT) |

|

43 |

R3 |

GPIO2_8 |

pr1_pru1_pru_r30_2 (Output) |

pr1_pru1_pru_r31_2 (INPUT) |

|

44 |

R4 |

GPIO2_9 |

pr1_pru1_pru_r30_3 (Output) |

pr1_pru1_pru_r31_3 (INPUT) |

|

45 |

R1 |

GPIO2_6 |

pr1_pru1_pru_r30_0 (Output) |

pr1_pru1_pru_r31_0 (INPUT) |

|

46 |

R2 |

GPIO2_7 |

pr1_pru1_pru_r30_1 (Output) |

pr1_pru1_pru_r31_1 (INPUT) |

PIN |

PROC |

NAME |

|||

|---|---|---|---|---|---|

17 |

A16 |

I2C1_SCL |

pr1_uart0_txd |

||

18 |

B16 |

I2C1_SDA |

pr1_uart0_rxd |

||

19 |

D17 |

I2C2_SCL |

pr1_uart0_rts_n |

||

20 |

D18 |

I2C2_SDA |

pr1_uart0_cts_n |

||

21 |

B17 |

UART2_TXD |

pr1_uart0_rts_n |

||

22 |

A17 |

UART2_RXD |

pr1_uart0_cts_n |

||

24 |

D15 |

UART1_TXD |

pr1_uart0_txd |

pr1_pru0_pru_r31_16 (Input) |

|

25 |

A14 |

GPIO3_21 |

pr1_pru0_pru_r30_5 (Output) |

pr1_pru0_pru_r31_5 (Input) |

|

26 |

D16 |

UART1_RXD |

pr1_uart0_rxd |

pr1_pru1_pru_r31_16 |

|

27 |

C13 |

GPIO3_19 |

pr1_pru0_pru_r30_7 (Output) |

pr1_pru0_pru_r31_7 (Input) |

|

28 |

C12 |

SPI1_CS0 |

eCAP2_in_PWM2_out |

pr1_pru0_pru_r30_3 (Output) |

pr1_pru0_pru_r31_3 (Input) |

29 |

B13 |

SPI1_D0 |

pr1_pru0_pru_r30_1 (Output) |

pr1_pru0_pru_r31_1 (Input) |

|

30 |

D12 |

SPI1_D1 |

pr1_pru0_pru_r30_2 (Output) |

pr1_pru0_pru_r31_2 (Input) |

|

31 |

A13 |

SPI1_SCLK |

pr1_pru0_pru_r30_0 (Output) |

pr1_pru0_pru_r31_0 (Input) |

Note

GPIO3_21 is also the 24.576MHZ clock input to the processor to enable HDMI audio. To use this pin the oscillator must be disabled.